37 RECEIVE-ONLY (RO) TELETYPEWRITER SET

FOR SWITCHED NETWORK SERVICE

WIRING DIAGRAM AND CIRCUIT DESCRIPTIONS

| CONTENTS                                           | PAGE |

|----------------------------------------------------|------|

| 1. GENERAL . . . . .                               | 1    |

| 2. WIRING DIAGRAM INDEX<br>(ATTACHMENTS) . . . . . | 1    |

1. GENERAL

1.01 This section is issued to provide actual and schematic wiring diagrams and detailed circuit description information for the 37 Receive-Only (RO) Teletypewriter Set (Figure 1).

1.02 Notes are included on the diagrams and explain the symbols used or point out special conditions that should be observed.

1.03 Most wiring diagrams (WDs) and wiring diagram circuit descriptions (WD-CDs) in this section are a part of one or more wiring diagram packages (WDPs). A complete listing of these WDs and WD-CDs is found on the attached WDP control sheets, and a numerical summary is included in the wiring diagram index.

2. WIRING DIAGRAM INDEX

(ATTACHMENTS)

Figure 1 - 37 RO Teletypewriter Set

| DRAWING NUMBER          | TITLE                                                                                                                                                                                                                                                                                                                                     |        |        |        |        |        |        |           |        |        |  |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|-----------|--------|--------|--|

| Wiring Diagram Packages |                                                                                                                                                                                                                                                                                                                                           |        |        |        |        |        |        |           |        |        |  |

| WDP0118                 | <p>Basic Wiring Diagram Package for 37 RO, KSR, and ASR Sets. It includes the following WDs and WD-CD:</p> <table><tbody><tr><td>8352WD</td><td>8360WD</td></tr><tr><td>8353WD</td><td>8361WD</td></tr><tr><td>8358WD</td><td>8365WD</td></tr><tr><td>8358WD-CD</td><td>303150</td></tr><tr><td>8359WD</td><td></td></tr></tbody></table> | 8352WD | 8360WD | 8353WD | 8361WD | 8358WD | 8365WD | 8358WD-CD | 303150 | 8359WD |  |

| 8352WD                  | 8360WD                                                                                                                                                                                                                                                                                                                                    |        |        |        |        |        |        |           |        |        |  |

| 8353WD                  | 8361WD                                                                                                                                                                                                                                                                                                                                    |        |        |        |        |        |        |           |        |        |  |

| 8358WD                  | 8365WD                                                                                                                                                                                                                                                                                                                                    |        |        |        |        |        |        |           |        |        |  |

| 8358WD-CD               | 303150                                                                                                                                                                                                                                                                                                                                    |        |        |        |        |        |        |           |        |        |  |

| 8359WD                  |                                                                                                                                                                                                                                                                                                                                           |        |        |        |        |        |        |           |        |        |  |

SECTION 574-300-400

WIRING DIAGRAM INDEX (continued)

| DRAWING NUMBER          | TITLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |        |        |        |           |           |        |        |           |           |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|--------|-----------|-----------|--------|--------|-----------|-----------|--------|--------|-----------|--------|--------|--------|-----------|--------|--------|--------|-----------|--------|--------|--------|-----------|--------|--------|--------|-----------|--------|

| Wiring Diagram Packages |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |        |        |        |           |           |        |        |           |           |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |

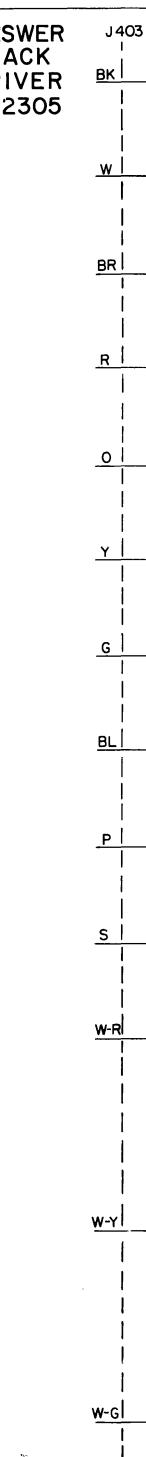

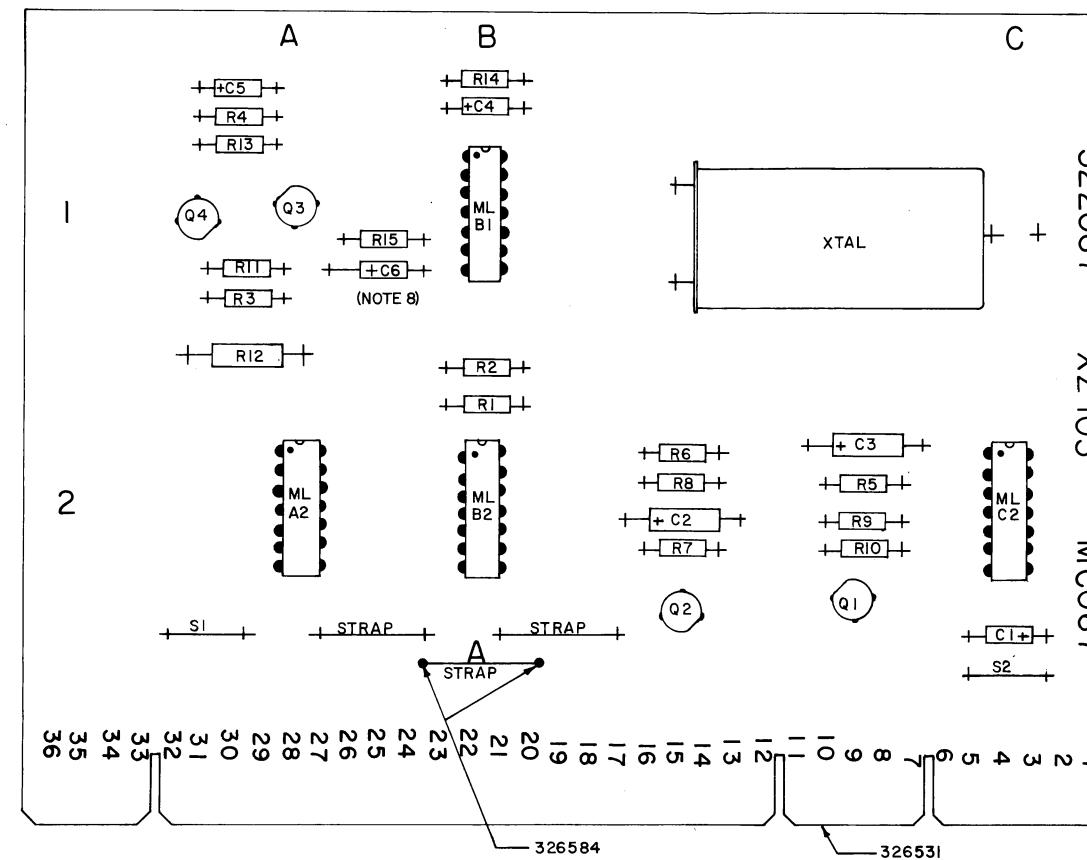

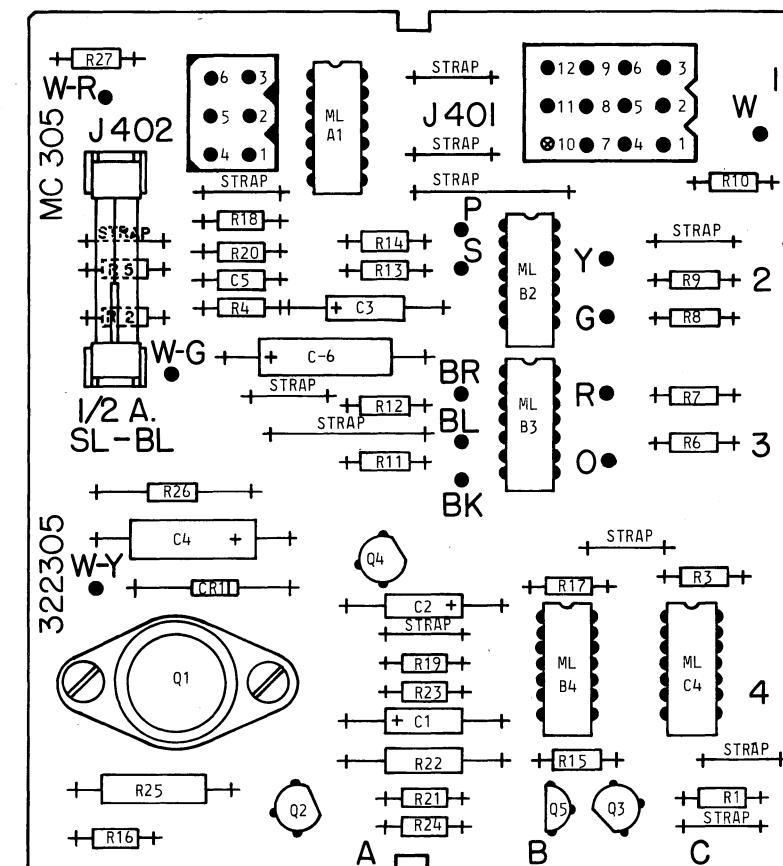

| WDP0125                 | <p>Wiring Diagram Package for Circuit Card Set TP332546 (RO). It includes the following WDs and WD-CDs:</p> <table><tbody><tr><td>7856WD</td><td>8399WD</td></tr><tr><td>8370WD</td><td>8773WD</td></tr><tr><td>8370WD-CD</td><td>8773WD-CD</td></tr><tr><td>8371WD</td><td>8774WD</td></tr><tr><td>8371WD-CD</td><td>8774WD-CD</td></tr><tr><td>8377WD</td><td>8845WD</td></tr><tr><td>8377WD-CD</td><td>303149</td></tr><tr><td>8383WD</td><td>322050</td></tr><tr><td>8383WD-CD</td><td>322059</td></tr><tr><td>8387WD</td><td>322062</td></tr><tr><td>8387WD-CD</td><td>322067</td></tr><tr><td>8388WD</td><td>322068</td></tr><tr><td>8388WD-CD</td><td>322070</td></tr><tr><td>8389WD</td><td>322304</td></tr><tr><td>8389WD-CD</td><td>322305</td></tr></tbody></table> | 7856WD | 8399WD | 8370WD | 8773WD | 8370WD-CD | 8773WD-CD | 8371WD | 8774WD | 8371WD-CD | 8774WD-CD | 8377WD | 8845WD | 8377WD-CD | 303149 | 8383WD | 322050 | 8383WD-CD | 322059 | 8387WD | 322062 | 8387WD-CD | 322067 | 8388WD | 322068 | 8388WD-CD | 322070 | 8389WD | 322304 | 8389WD-CD | 322305 |

| 7856WD                  | 8399WD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |        |        |        |           |           |        |        |           |           |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |

| 8370WD                  | 8773WD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |        |        |        |           |           |        |        |           |           |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |

| 8370WD-CD               | 8773WD-CD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        |        |        |        |           |           |        |        |           |           |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |

| 8371WD                  | 8774WD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |        |        |        |           |           |        |        |           |           |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |

| 8371WD-CD               | 8774WD-CD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        |        |        |        |           |           |        |        |           |           |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |

| 8377WD                  | 8845WD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |        |        |        |           |           |        |        |           |           |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |

| 8377WD-CD               | 303149                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |        |        |        |           |           |        |        |           |           |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |

| 8383WD                  | 322050                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |        |        |        |           |           |        |        |           |           |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |

| 8383WD-CD               | 322059                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |        |        |        |           |           |        |        |           |           |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |

| 8387WD                  | 322062                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |        |        |        |           |           |        |        |           |           |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |

| 8387WD-CD               | 322067                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |        |        |        |           |           |        |        |           |           |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |

| 8388WD                  | 322068                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |        |        |        |           |           |        |        |           |           |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |

| 8388WD-CD               | 322070                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |        |        |        |           |           |        |        |           |           |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |

| 8389WD                  | 322304                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |        |        |        |           |           |        |        |           |           |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |

| 8389WD-CD               | 322305                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |        |        |        |           |           |        |        |           |           |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |        |        |           |        |

|   | 1   | 2                                                                                                                                                                                                                                                                                                                                                            | 3                           | 4                                                   | 5                 | 6                                                                                                                                                                                         | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8                                               | 9                                    |

|---|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--------------------------------------|

|   |     |                                                                                                                                                                                                                                                                                                                                                              |                             |                                                     |                   |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                 |                                      |

|   | NO. | NOTES                                                                                                                                                                                                                                                                                                                                                        |                             |                                                     |                   |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                 | 7856 WD                              |

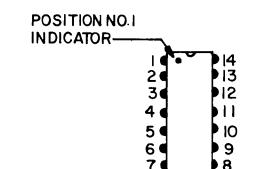

| 1 |     | THE FOLLOWING PROCEDURE SHOULD BE FOLLOWED WHEN INSTALLING CIRCUIT CARD OPTIONS:<br>A. TURN POWER OFF<br>B. LOCATE CARD POSITION GIVEN IN INSTALLATION PROCEDURE.<br>C. CHECK POLARITY OF CARDS(NOTCHES) AGAINST POLARITY OF CARD CONNECTOR.(SMALL TAB IN CONNECTOR)<br>D. INSTALL CARD.                                                                     |                             |                                                     |                   |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                 | REVISIONS                            |

|   |     | SERVICE UNIT OPTION ARRANGEMENTS                                                                                                                                                                                                                                                                                                                             | DESCRIPTION                 | APPLICATION                                         | ASSEMBLY AFFECTED | INSTALLATION PROCEDURE                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                 | ISSUE DATE AUTH. NO.                 |

| 1 |     |                                                                                                                                                                                                                                                                                                                                                              | CHARACTER COUNTER & CONTROL | ASR                                                 | 322045            | INSTALL PIGGY-BACK ON CARD ASSEMBLY 322045 POSITION XZ 301.<br>1. REMOVE STRAP "A" WHEN "NU-LINE" IS NOT IMPLEMENTED IN PRINTER.                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1 11-21-68 19778 R                              |                                      |

| 2 |     | X                                                                                                                                                                                                                                                                                                                                                            |                             |                                                     | 322055            | INSTALL IN POSITION XZ 303.<br>1. PROGRAM PI-P24 FOR A COUNT OF 66 AS FOLLOWS, STRAP P3-P18, P6-P19, P8-P20, P10-P21, P12-P22, P13-P23, P2-P17<br>2. FOR OTHER COUNTS REFER TO 8380WD-CD. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2 3-17-69 96904                                 |                                      |

| 2 |     | THE FOLLOWING PROCEDURE SHOULD BE FOLLOWED WHEN INSTALLING CABLE OPTIONS:<br>A. TURN POWER OFF.<br>B. IDENTIFY WIRES AND TERMINALS TO BE CONNECTED PER INSTALLATION PROCEDURE.<br>C. INSTALL PUSH-ON TERMINAL CONTACTS DIRECTLY OVER ALLOTTED TERMINALS ON WIRING FIELD TERMINAL BOARD.<br>D. DO NOT SHORT OR BEND TERMINALS ON WIRING FIELD TERMINAL BOARD. | X                           | IO/II UNIT CODE 150 WPM.                            | RO/KSR ASR        | 322067<br>322066                                                                                                                                                                          | PROGRAM CIRCUIT CARD ASSEMBLY AFFECTED.<br>POSITION XZ 105 AS FOLLOWS:<br>1. IO UNIT DO NOT REMOVE STRAP "A".                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                 | 3 II-17-69 99693                     |

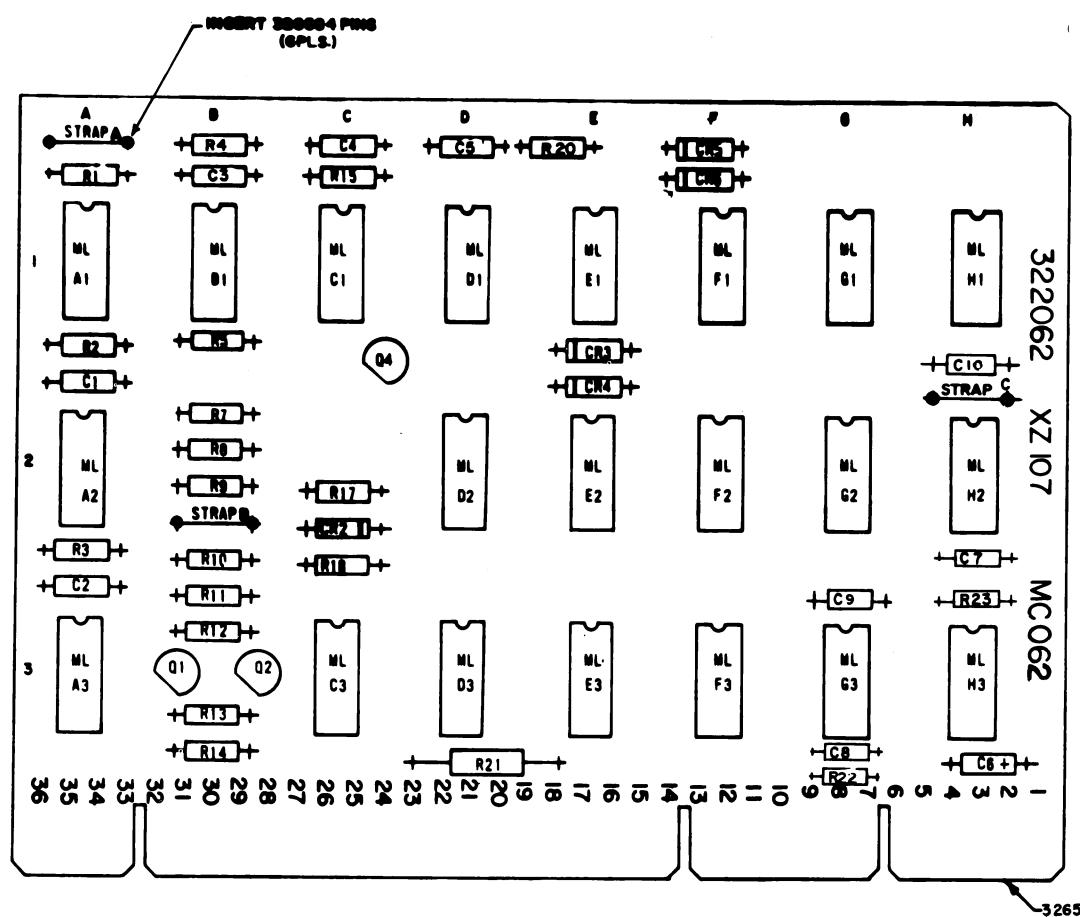

| 3 |     | X                                                                                                                                                                                                                                                                                                                                                            |                             | HALF & FULL DUPLEX                                  | KSR/ASR           | 322062                                                                                                                                                                                    | PROGRAM CIRCUIT CARD ASSEMBLY AFFECTED<br>POSITION XZ 107 AS FOLLOWS:(FIELD MODIFICATION ONLY,CARD TO BE SHIPPED WITH ALL STRAPS.<br>1. DEDICATED HALF DUPLEX-REMOVE STRAPS "B"<br>2. DEDICATED FULL DUPLEX-REMOVE STRAPS "A"<br>3. LINE CONTROL OPERATION- REMOVE STRAPS "A, B & C"<br>4. CHECK MECHANICAL PORTIONS OF STUNT BOX FOR APPROPRIATE CODES.                                                                                                                                                                                                             |                                                 | 4 4-14-70 94                         |

| 4 |     | X                                                                                                                                                                                                                                                                                                                                                            |                             | RECEIVER STATUS ALARM                               | KSR/ASR           | 322062                                                                                                                                                                                    | I. REMOVE STRAP "C"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                 |                                      |

| 5 |     | X                                                                                                                                                                                                                                                                                                                                                            |                             | MOTOR CONTROL (DATAPHONE) EOT AND ALARM DISCONNECT. | RO/KSR/ASR        | 322068                                                                                                                                                                                    | PROGRAM CIRCUIT CARD ASSEMBLY AFFECTED<br>POSITION XZ 109 AS FOLLOWS:<br>1. REMOVE STRAPS "D, E, G, H, K, M, Y"<br>DO NOT REMOVE STRAPS "A, B, C, F, L".                                                                                                                                                                                                                                                                                                                                                                                                             |                                                 |                                      |

|   |     | X                                                                                                                                                                                                                                                                                                                                                            |                             | AUTOMATIC READER AND PUNCH CONTROL.                 | ASR               | 322079                                                                                                                                                                                    | I. INSTALL CIRCUIT CARD ASSEMBLY IN POSITION XZ 304.<br>2. PROGRAM CONTROL PANEL PER 8365 WD.<br>3. CHECK MECHANICAL PORTIONS OF STUNT BOX FOR APPROPRIATE CODES.                                                                                                                                                                                                                                                                                                                                                                                                    |                                                 |                                      |

|   |     |                                                                                                                                                                                                                                                                                                                                                              |                             |                                                     |                   | 322054                                                                                                                                                                                    | REMOVE STRAP "A" OF CIRCUIT CARD ASSEMBLY POSITION XZ108 OF R-T ELECTRICAL SERVICE UNIT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                 | DP                                   |

|   |     | X                                                                                                                                                                                                                                                                                                                                                            |                             | TWO COLOR RIBBON.                                   | RO/KSR/ASR        | 322070                                                                                                                                                                                    | I. INSTALL CIRCUIT CARD ASSEMBLY AFFECTED IN POSITION XZ 405.<br>2. CHECK PRINTER AND STUNT BOX FOR APPROPRIATE MECHANISM & CODES.                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                 |                                      |

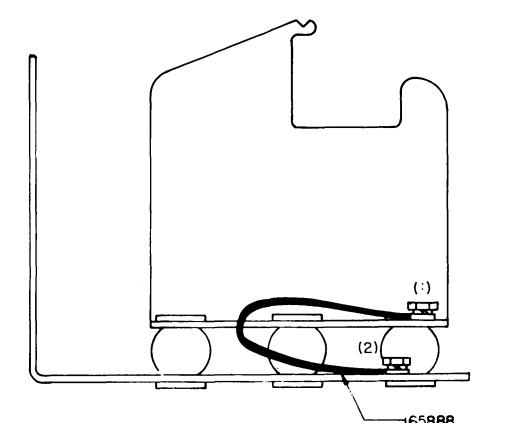

|   |     | X                                                                                                                                                                                                                                                                                                                                                            |                             | ANSWER BACK<br>INSTALLATION KIT. FOR THE YAB 802    | RO/KSR/ASR        | 327801<br>336926                                                                                                                                                                          | I. INSTALL THIS SELF CONTAINED ASSEMBLY IN POSITIONS XZ 310-XZ 315.<br>2. INSTALL CABLE ASSEMBLY 326575 AS FOLLOWS:<br><br>WIRE COLOR<br>WHITE - BROWN<br>WHITE - RED<br>WHITE - ORANGE<br>WHITE - YELLOW<br>WHITE - GREEN<br>WHITE - BLUE<br>WHITE - PURPLE<br>WHITE - SLATE<br>WHITE - BLACK<br>GREEN - SLATE<br>BLUE - GREEN<br>ORANGE - GREEN<br>RED - BLUE<br>YELLOW<br>GREEN<br>BLACK<br>BLUE<br>BROWN<br>BROWN<br><br>TBIII CONNECTION.<br>A1<br>A2<br>A3<br>A4<br>A5<br>A6<br>A7<br>A8<br>A11<br>J3<br>H3<br>F3<br>C3<br>A13<br>A14<br>G3<br>A10<br>D3<br>E3 |                                                 | MODEL 37<br>OPTION<br>ANALYSIS CHART |

|   |     | X                                                                                                                                                                                                                                                                                                                                                            |                             | CONTROL CHARACTER INHIBIT                           | KSR/ASR           | 322059                                                                                                                                                                                    | INSTALL STRAP 327842 BETWEEN PINS 2 AND 7 ON CARD CONNECTOR XZ 102.<br>INSTALL STRAP 327842 BETWEEN PIN B26 ON CARD CONNECTOR XZ102 AND PIN 2 ON CARD CONNECTOR XZ 305.                                                                                                                                                                                                                                                                                                                                                                                              |                                                 | APPROVALS                            |

|   |     |                                                                                                                                                                                                                                                                                                                                                              |                             |                                                     |                   |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | D AND R E OF M<br><i>SL</i> <i>SL</i> <i>SL</i> |                                      |

|   |     |                                                                                                                                                                                                                                                                                                                                                              |                             |                                                     |                   |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | E-NUMBER<br>PROD. NO. 7856 WD                   |                                      |

|   |     |                                                                                                                                                                                                                                                                                                                                                              |                             |                                                     |                   |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DATE 9-4-68                                     |                                      |

|   |     |                                                                                                                                                                                                                                                                                                                                                              |                             |                                                     |                   |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | P.D. FILE NO. G-A354AA                          |                                      |

|   |     |                                                                                                                                                                                                                                                                                                                                                              |                             |                                                     |                   |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DRAWN W.P.B CHKD <i>SL</i>                      |                                      |

|   |     |                                                                                                                                                                                                                                                                                                                                                              |                             |                                                     |                   |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ENGD. M.J.R. APPD. <i>SL</i>                    |                                      |

|   |     |                                                                                                                                                                                                                                                                                                                                                              |                             |                                                     |                   |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TELETYPE CORPORATION                            |                                      |

|   |     |                                                                                                                                                                                                                                                                                                                                                              |                             |                                                     |                   |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7856 WD                                         |                                      |

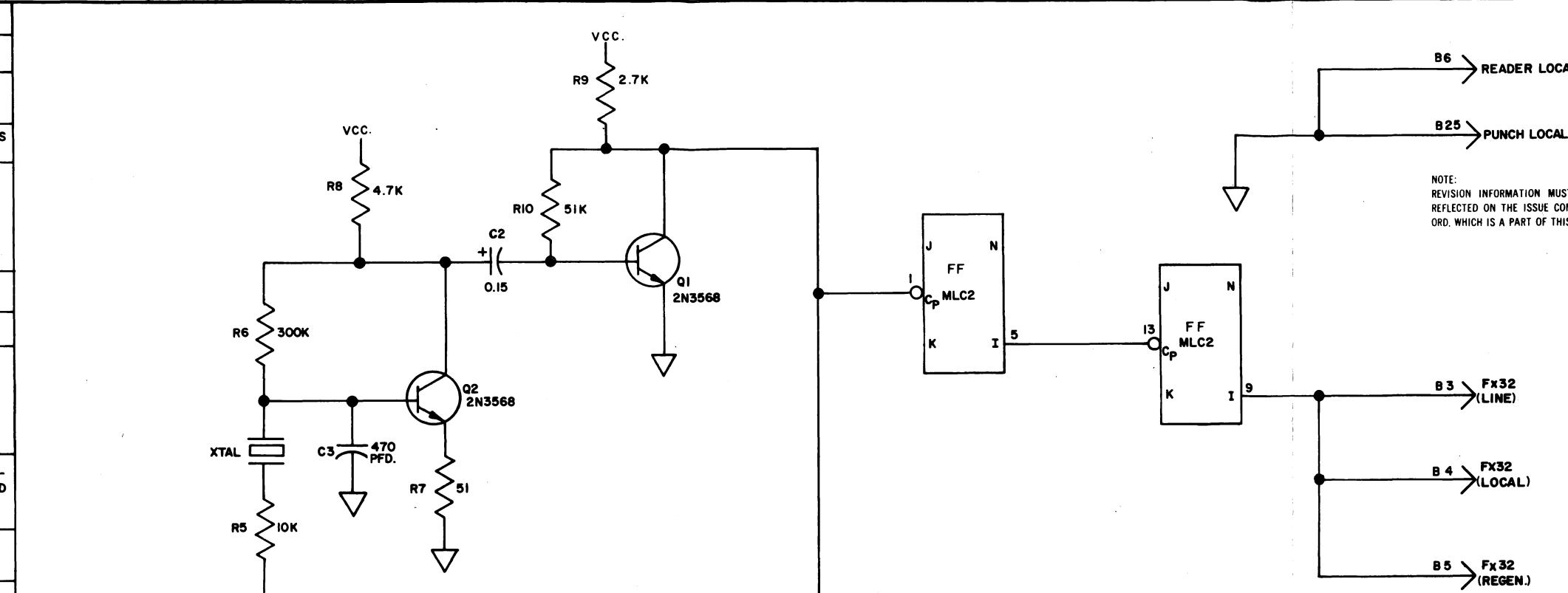

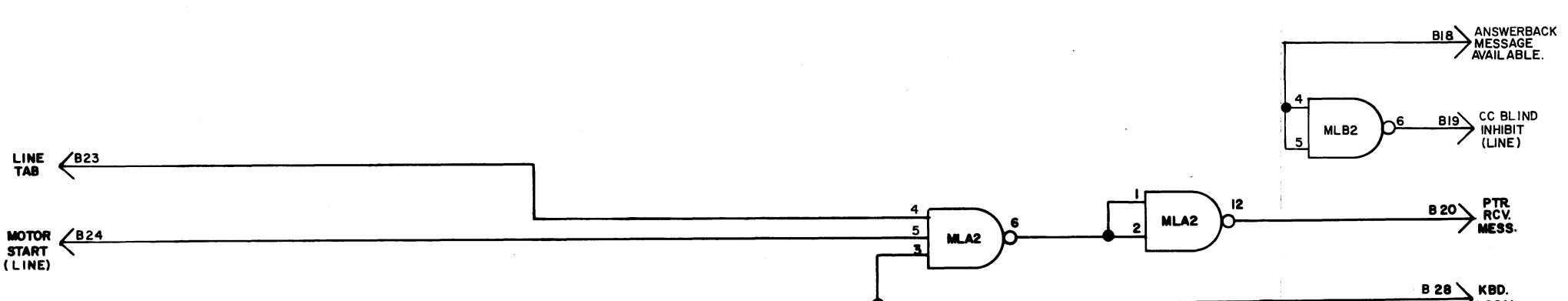

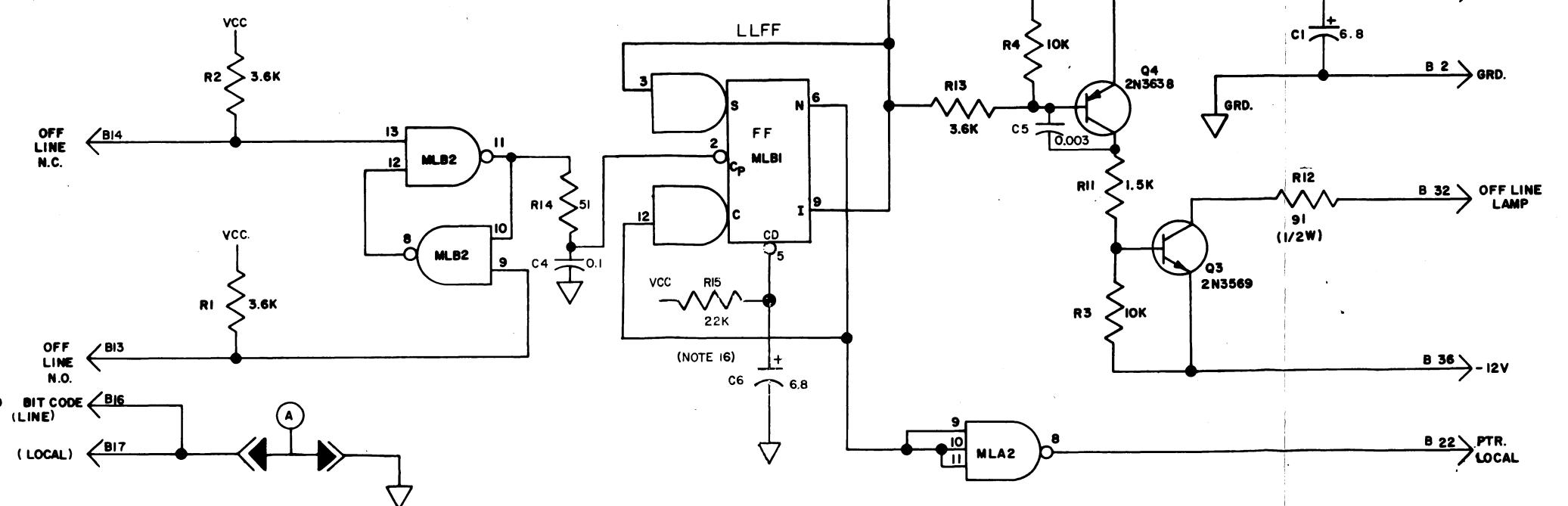

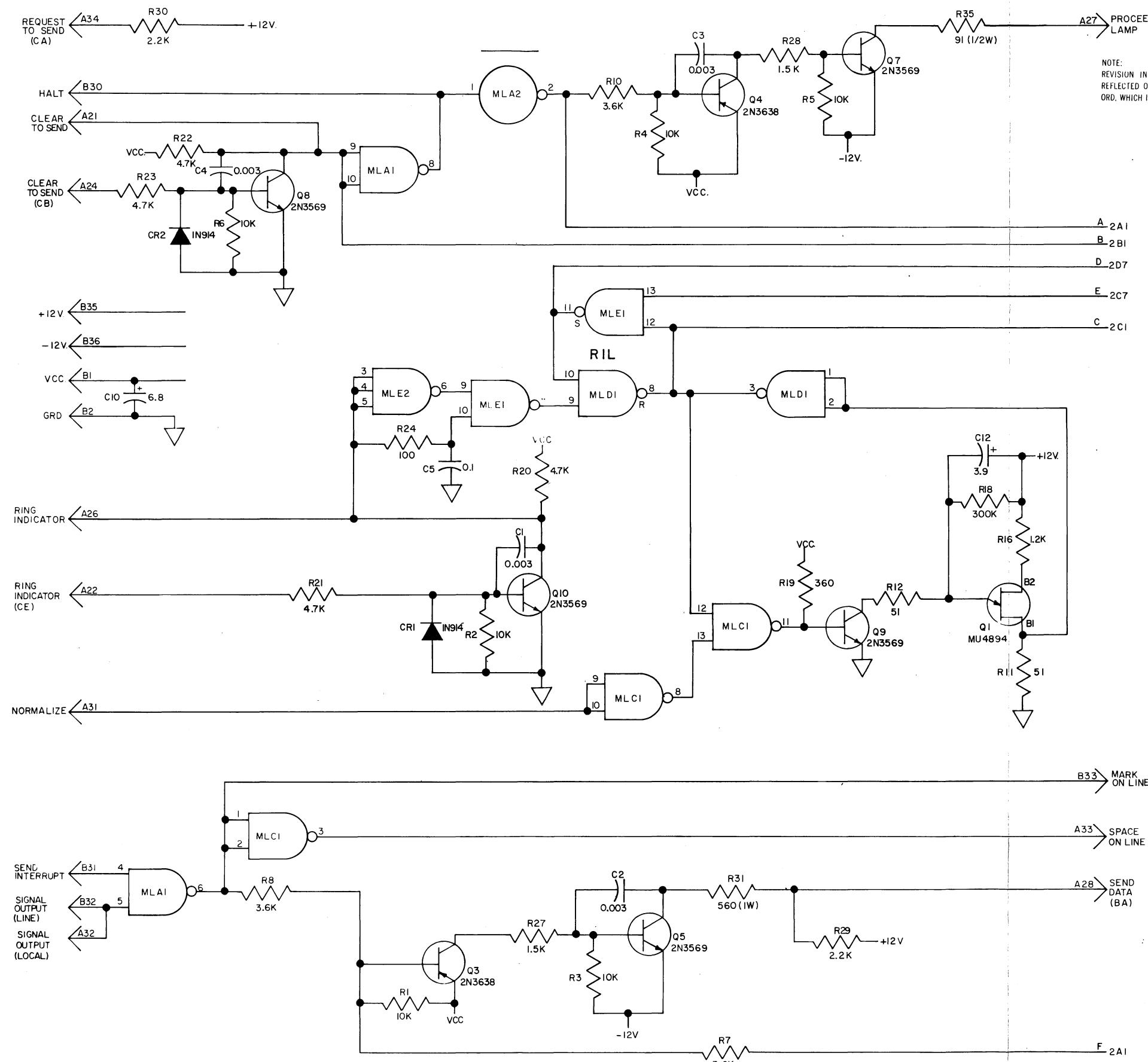

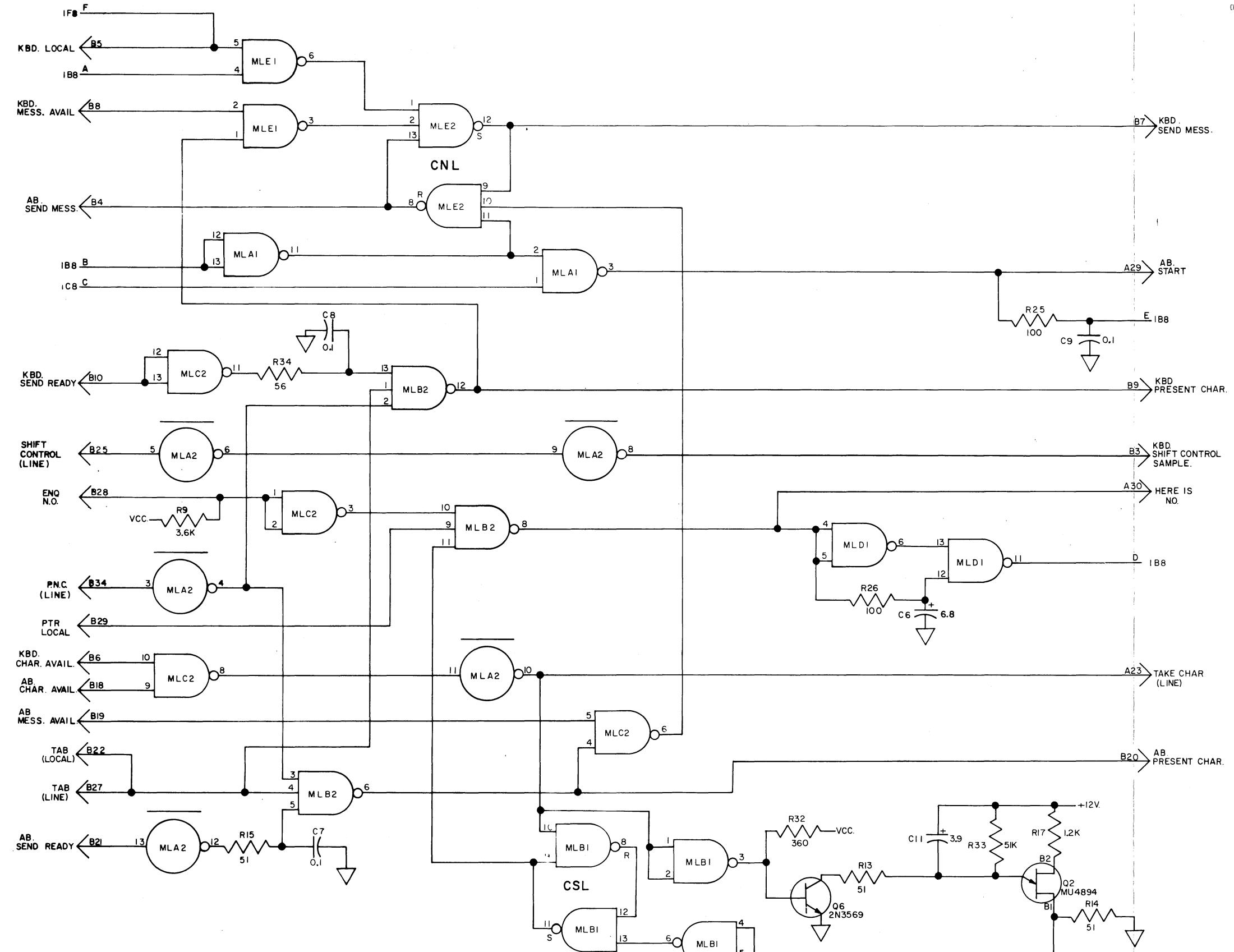

8370WD

## REVISIONS

| ISSUE | DATE    | AUTH. NO. |

|-------|---------|-----------|

| 1     | 9-25-68 | 19568-R   |

|       |         |           |

|       |         |           |

|       |         |           |

NOTE:

REVISION INFORMATION MUST ALSO BE

REFLECTED ON THE ISSUE CONTROL REC-

ORD, WHICH IS A PART OF THIS DRAWING.

SEE ISSUE CONTROL RECORD FOR COM-

PIECE LIST OF SHEETS COMPRISING THIS

W.D.

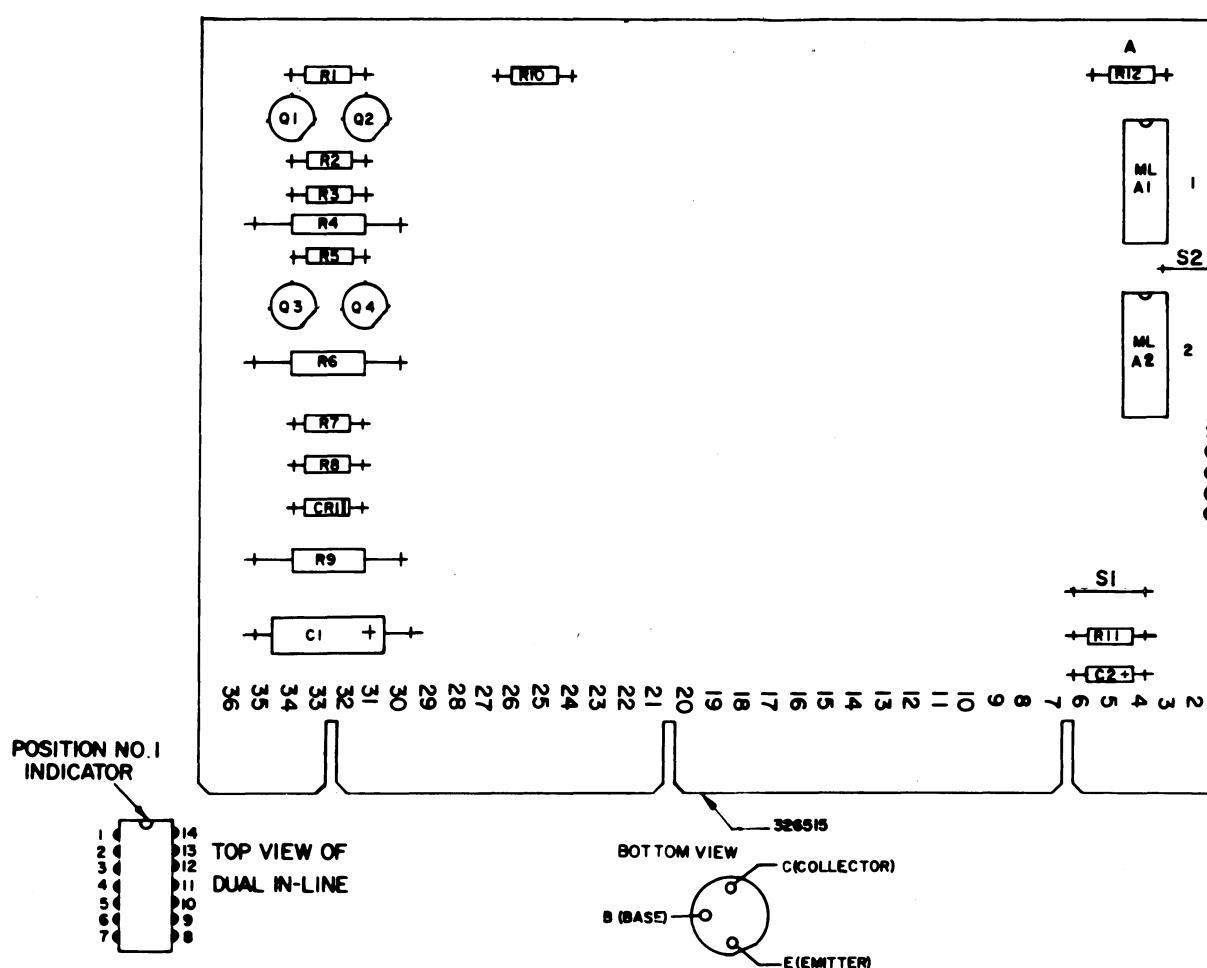

SHEET -1

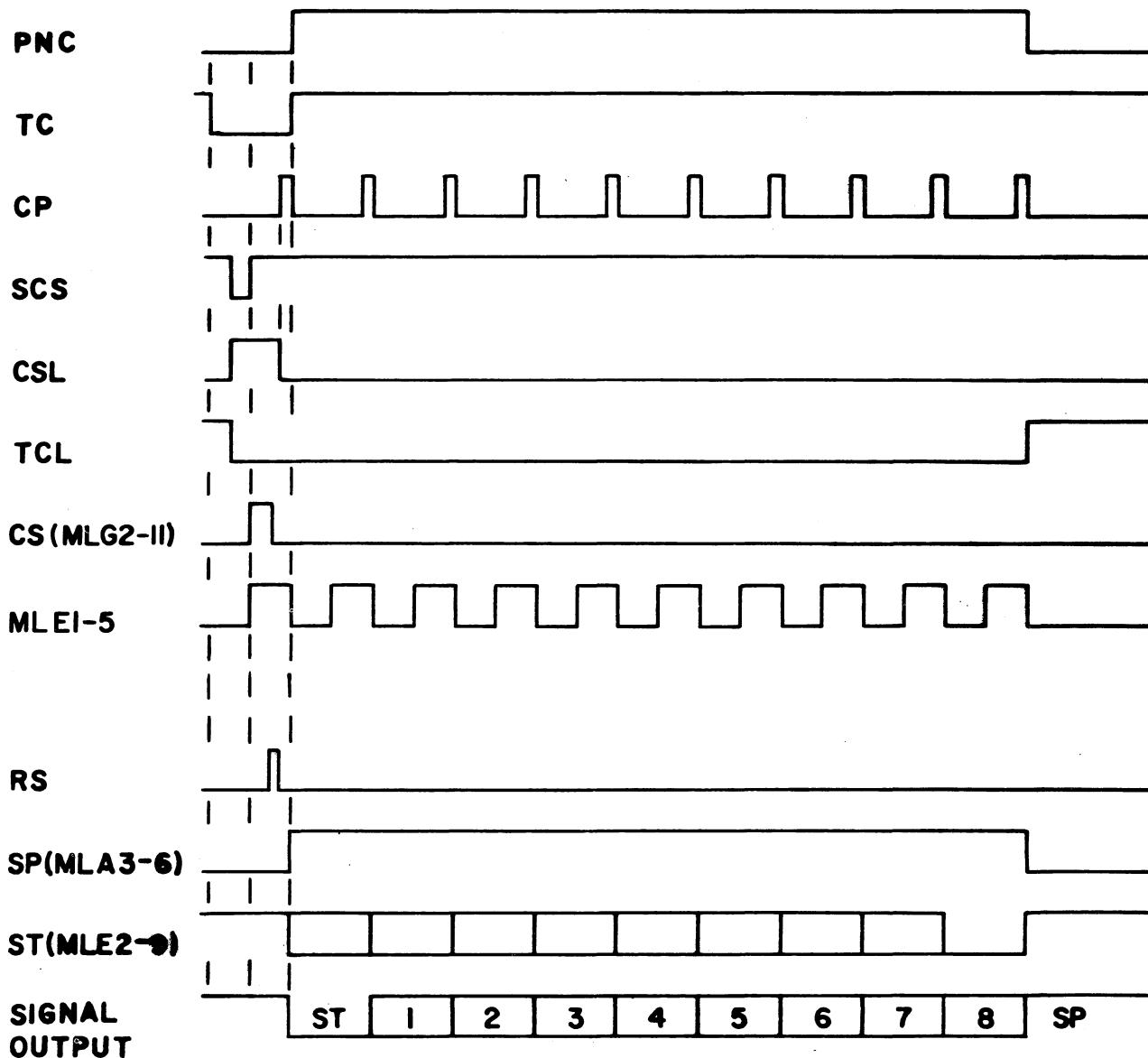

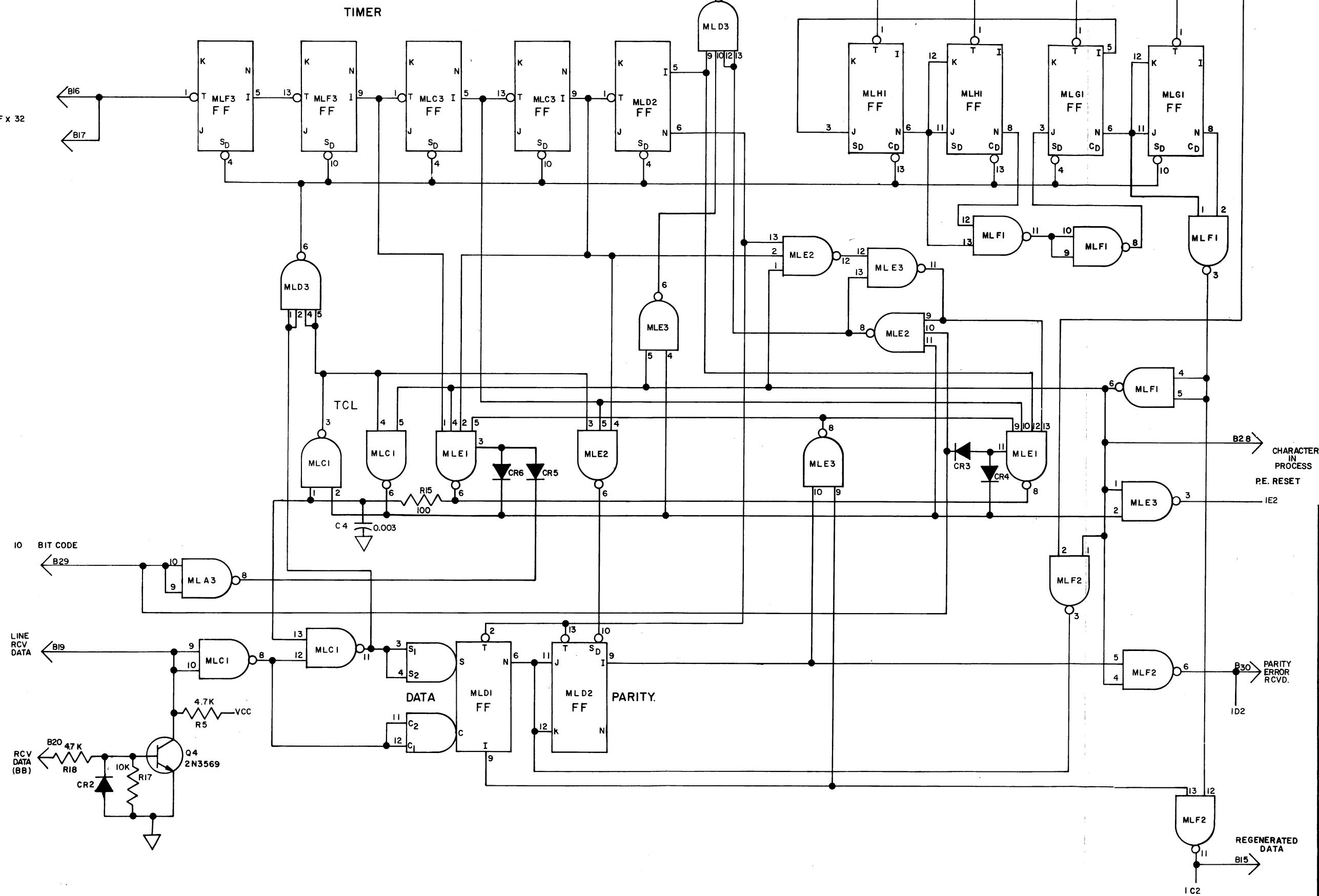

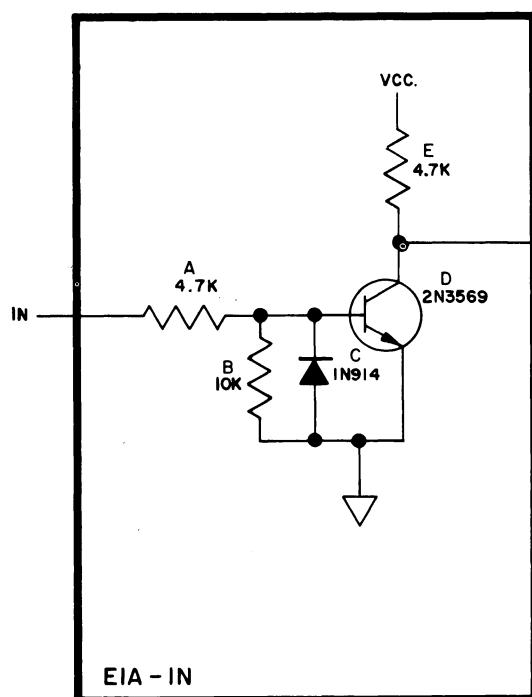

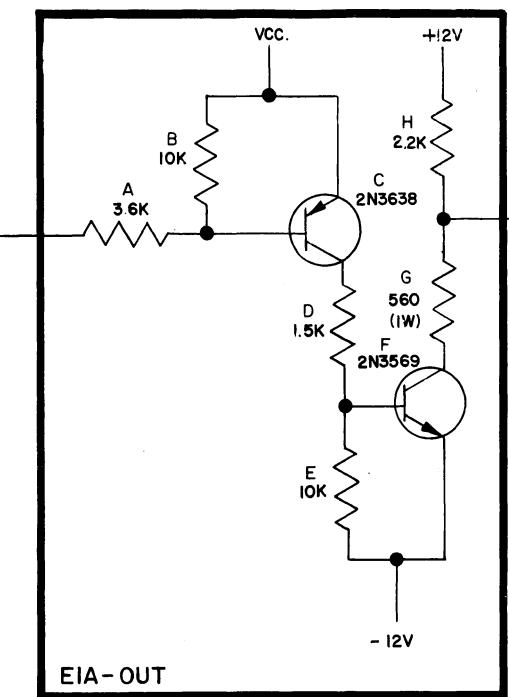

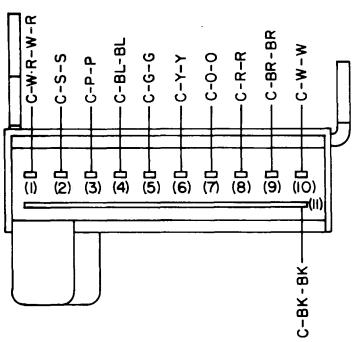

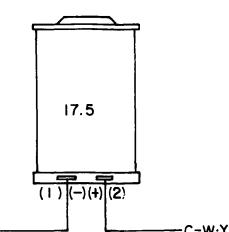

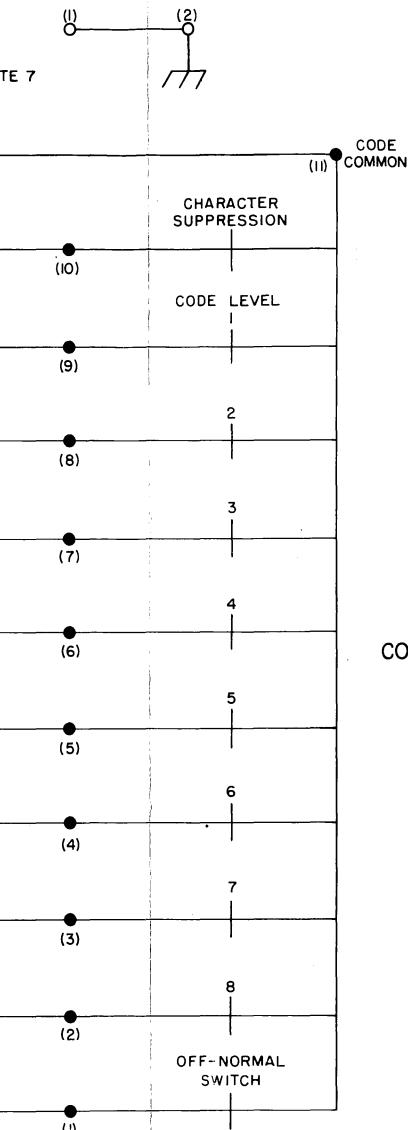

SCHEMATIC

WIRING DIAGRAM

FOR

RECEIVING DEVICE

## APPROVALS

| D AND R                 | E OF M                    |

|-------------------------|---------------------------|

| <i>[Signature]</i>      | <i>[Signature]</i>        |

| E-NUMBER                |                           |

| PROD. NO. 8370 WD.      |                           |

| DATE 2-29-68            |                           |

| P.D. FILE NO. G-A354 AA |                           |

| DRAWN W.P.B.            | CHKD. <i>[Signature]</i>  |

| ENG'D. C.A.Y.           | APP'D. <i>[Signature]</i> |

TELETYPE

CORPORATION

8370WD

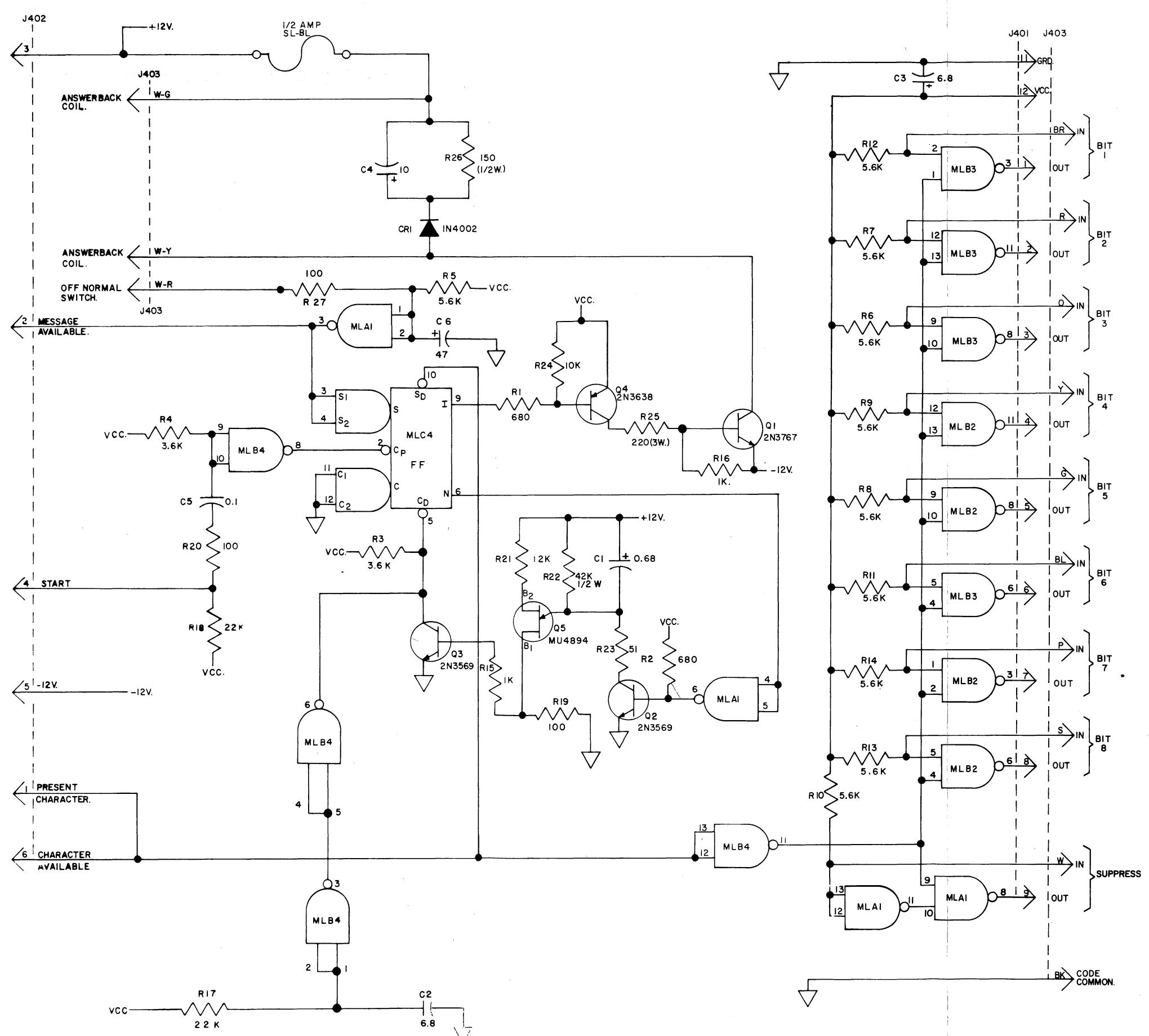

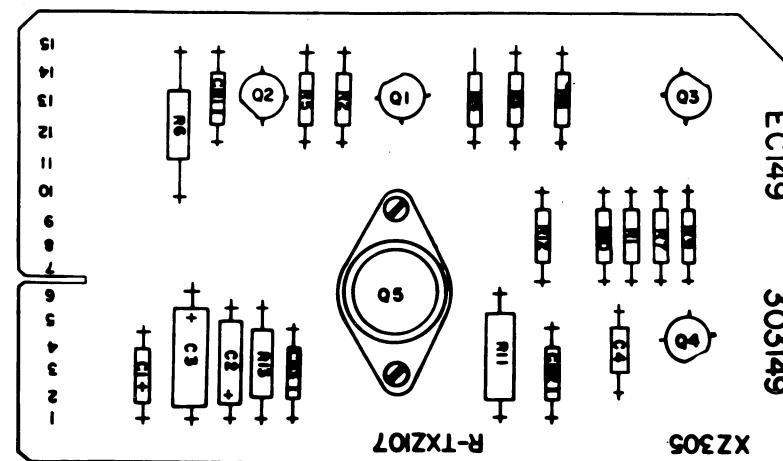

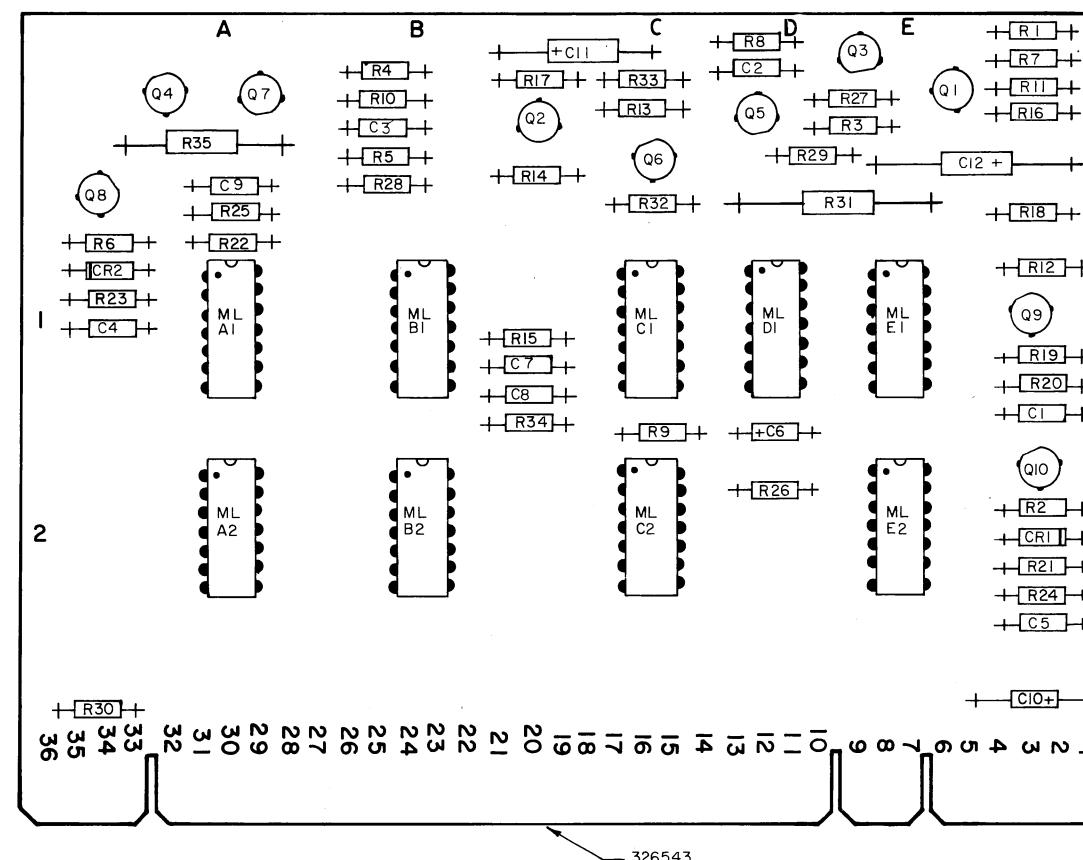

CIRCUIT DESCRIPTION OF THE RECEIVING DEVICE LOGIC CARD

(ASSEMBLY NUMBER 303149)

TABLE OF CONTENTS

| <u>SECTION</u> | <u>DESCRIPTION</u>                           | <u>TOTAL PAGES<br/>IN SECTION</u> |

|----------------|----------------------------------------------|-----------------------------------|

| I              | General Technical Information                | 2                                 |

| II             | Detailed Description and Theory of Operation | 1                                 |

NOTE: REVISION INFORMATION MUST ALSO BE REFLECTED ON THE ISSUE CONTROL RECORD, WHICH IS A PART OF THIS DRAWING.

SEE ISSUE CONTROL RECORD FOR COMPLETE LIST OF SHEETS COMPRISING THIS W.D.

CIRCUIT DESCRIPTION OF THE RECEIVING DEVICE LOGIC CARD

(ASSEMBLY NUMBER 303149)

SECTION I

GENERAL TECHNICAL DATA

1. BASIC FUNCTION

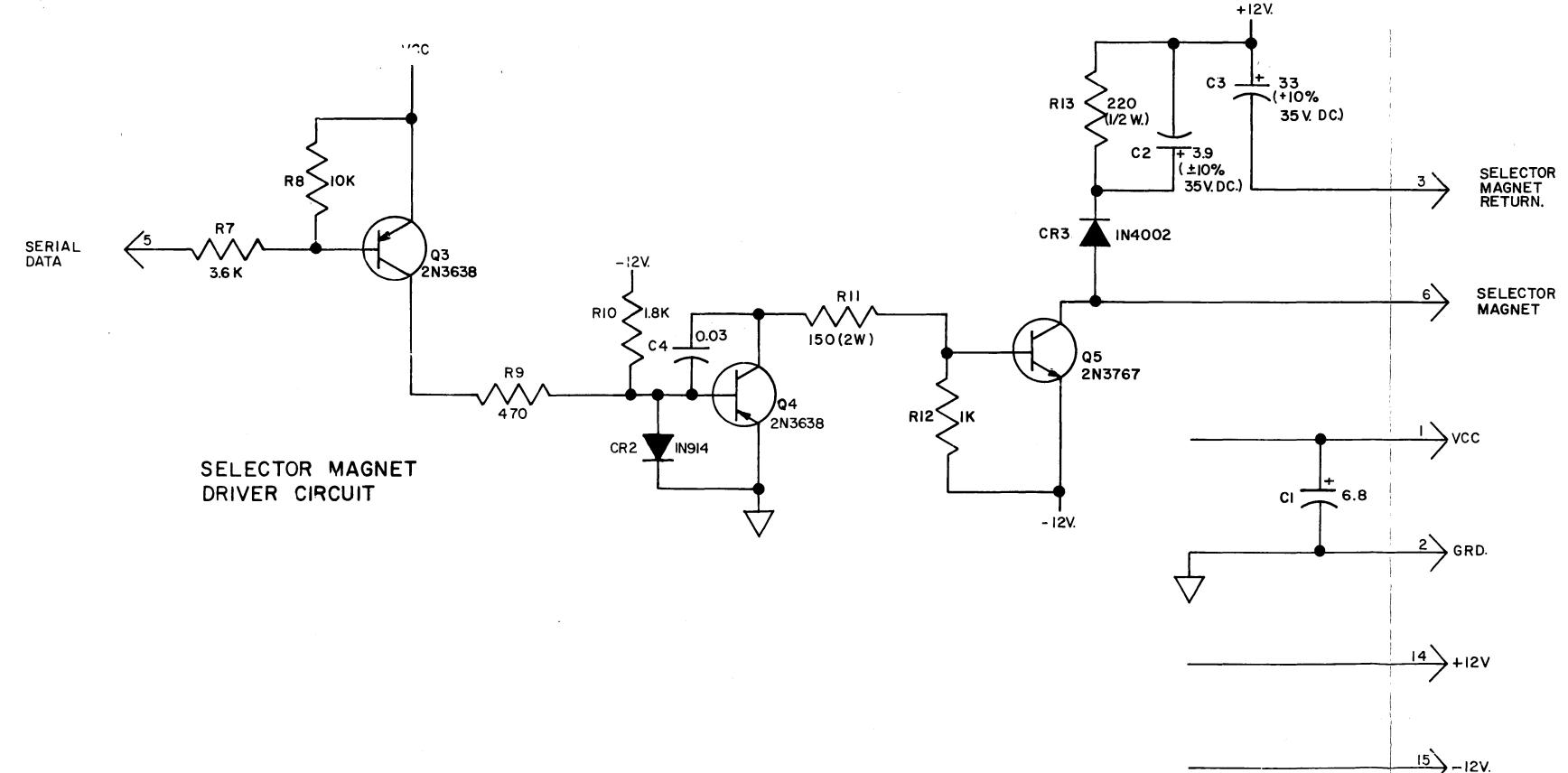

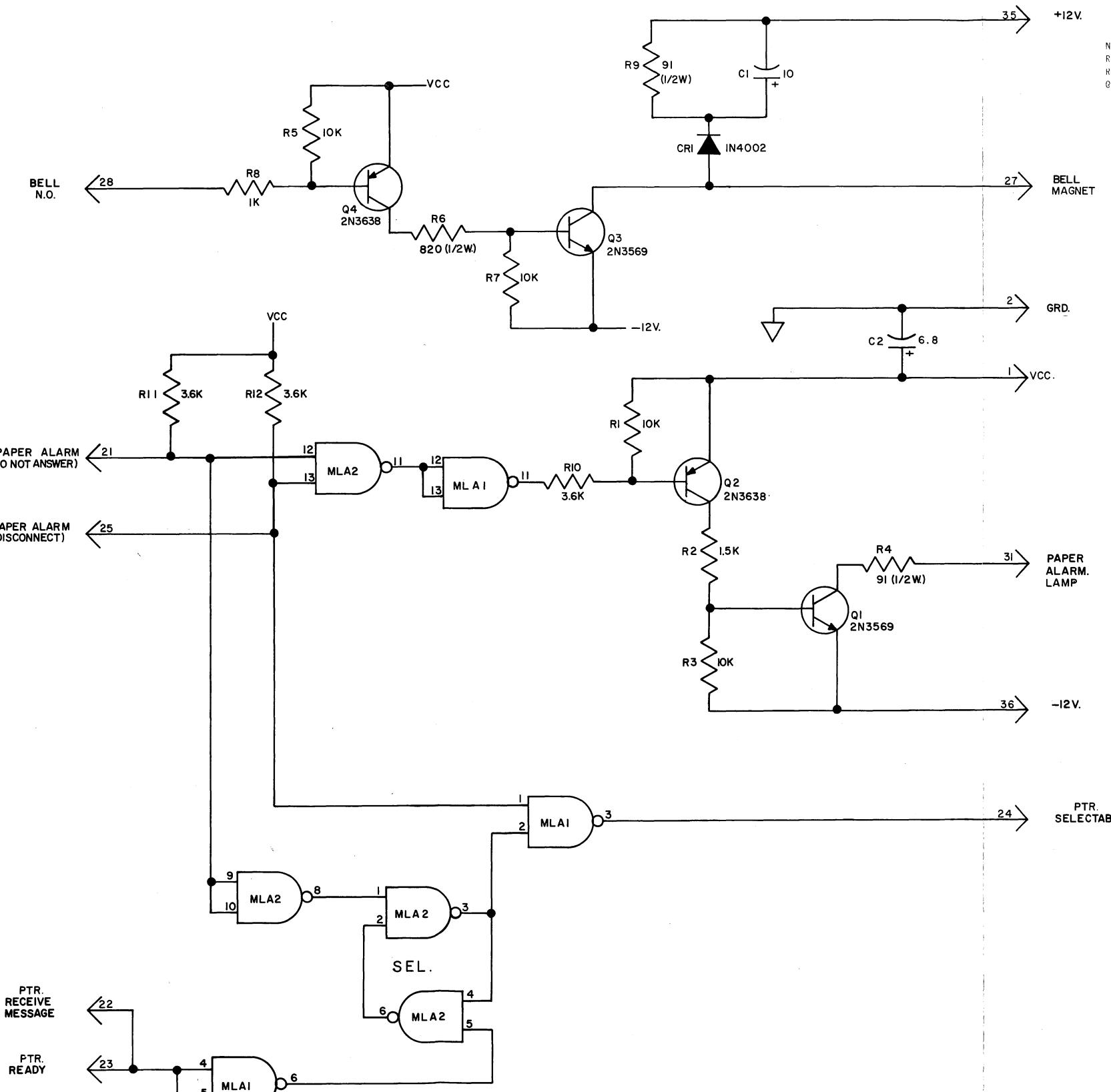

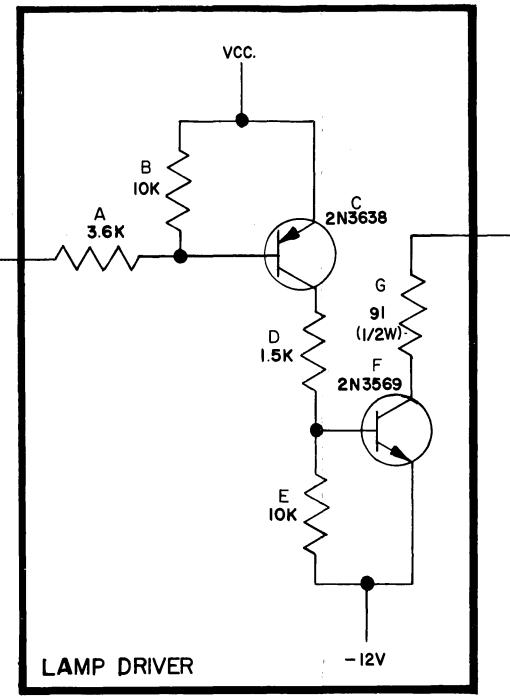

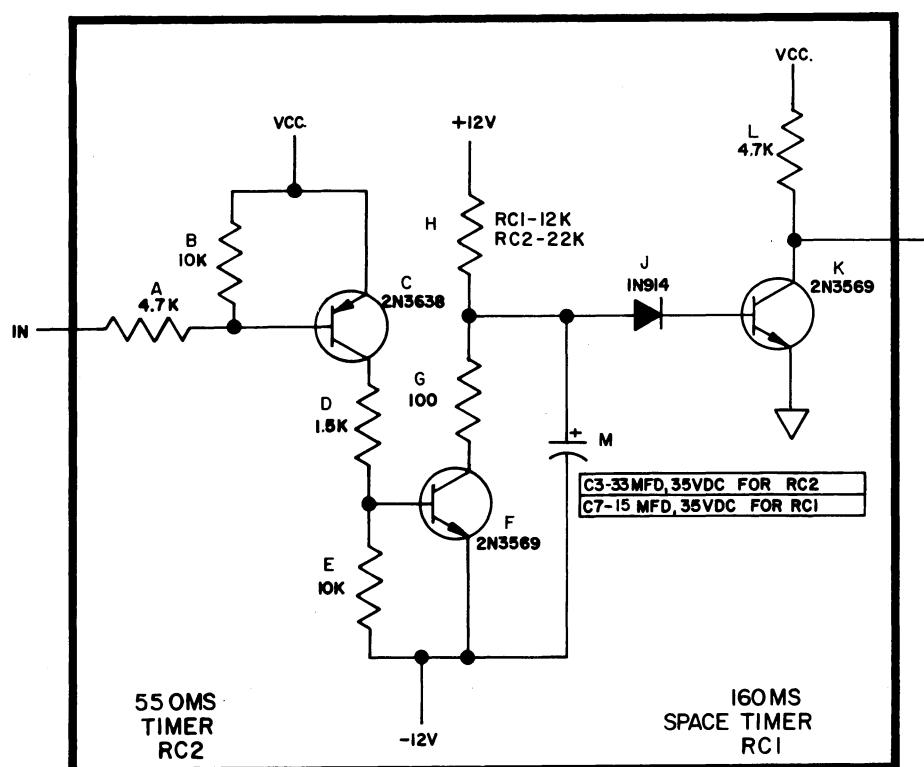

1.1 The 303149 Receiving Device Logic card combines the function of a selector magnet driver and a motor control relay driver.

1.2 Selector Magnet Driver

The selector magnet driver sinks a steady state current of up to 600 ma DC on a MARK input and sinks zero current on a SPACE input. The MARK input is a logic one, and a SPACE input is a logical zero.

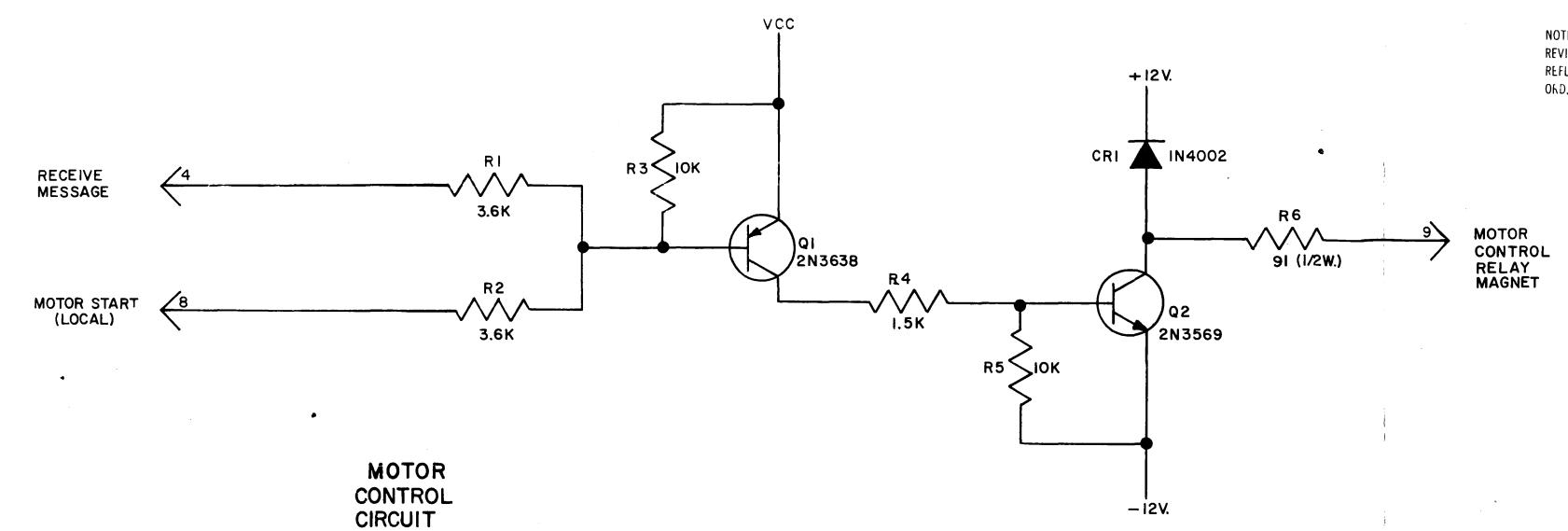

1.3 Motor Control

The motor control relay driver is capable of supplying a current of 40 to 60 ma to operate the motor control relay. The relay will be operated on a logic zero input and released on a logic one input.

2. GENERAL TECHNICAL DATA

2.1 Input-Output Data

2.1.1 The Receiving Device Logic card converts the integrated circuit logic levels to current levels appropriate for magnet operation.

A logic one is defined as a voltage level between 5.0 Volts and 6.6 Volts (usually a logic one approximates the integrated circuit supply voltage). A logic one draws no current from the input of the logic element.

Signal voltages between circuit ground potential and +0.5 Volts are considered logic zero.

2.2 Input-Output Characteristics

Motor Control

2.2.1 Receive Message/Motor Start Local (Pins 4 and 8)

These two inputs are connected together in a logical or configuration. A logic zero input will energize the associated motor control relay. Input impedance is 3.6K.

2.2.2 Motor Control Relay Magnet (Pin 9)

The associated motor control relay is connected to this output (typical coil resistance 430 ohms). The output impedance is 91 ohms in series with a -12 Volts. The relay driver output is capable of supplying up to 60 ma of current. Relay magnet drop-out is diode suppressed.

Selector Magnet Driver

2.2.3 Send Data (Pin 5)

Under the control of set logic this input is supplied with MARK and SPACE signals corresponding to received data. A logic one signal (MARK) will cause the selector magnet to be energized. A logic zero signal (SPACE) will de-energize the selector magnet. Input and impedance is 3.6K.

2.2.4 Selector Magnet (Pin 6)

The negative end of the selector magnet is connected to this output which will establish a discharge path through a Diode coupled resistor capacitor network. Typical dropout time is approximately 2.50 milliseconds.

2.2.5 Selector Magnet Return (Pin 3)

The positive end of the selector magnet is connected to this output. In series with the selector-coil is a parallel resistor capacitor network which permits maximum current through the coil during SPACE to MARK transitions. Typical MARK hold current is approximately 600 milliamperes. Nominal rise time is 2.25 milliseconds. Typical load supplied is 3.5 ohms 20 millihenries inductance.

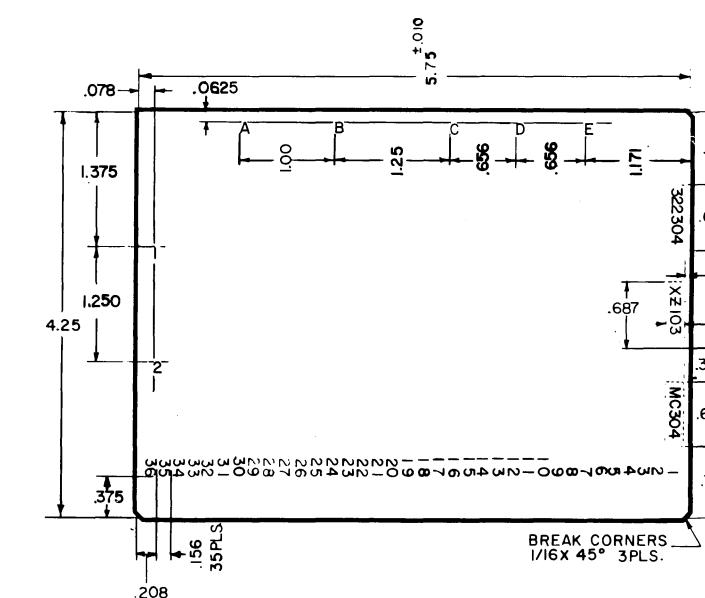

2.3 Mechanical Requirements

The motor control amplifier and the selector magnet driver are mounted on a 15-pin circuit board.

2.4 Power Requirements

| <u>D.C. Supply</u>               | <u>Current Required</u> |

|----------------------------------|-------------------------|

| +5.0V to +5.50V (+5.25V Nom.)    | 0 to 20 ma              |

| +11.65 to +13.75V (+12.5V Nom.)  | 0 to 660 ma             |

| -11.13V to -13.88V (-12.5V Nom.) | 0 to 660 ma             |

2.5 Operating Temperature Range

0°C to 70°C (in free air)

2.6 Storage Temperature Range

-40°C to 70°C

NOTE: REVISION INFORMATION MUST ALSO BE REFLECTED ON THE ISSUE CONTROL RECORD, WHICH IS A PART OF THIS DRAWING.

SEE ISSUE CONTROL RECORD FOR COMPLETE LIST OF SHEETS COMPRISING THIS DRAWING.

W.D.

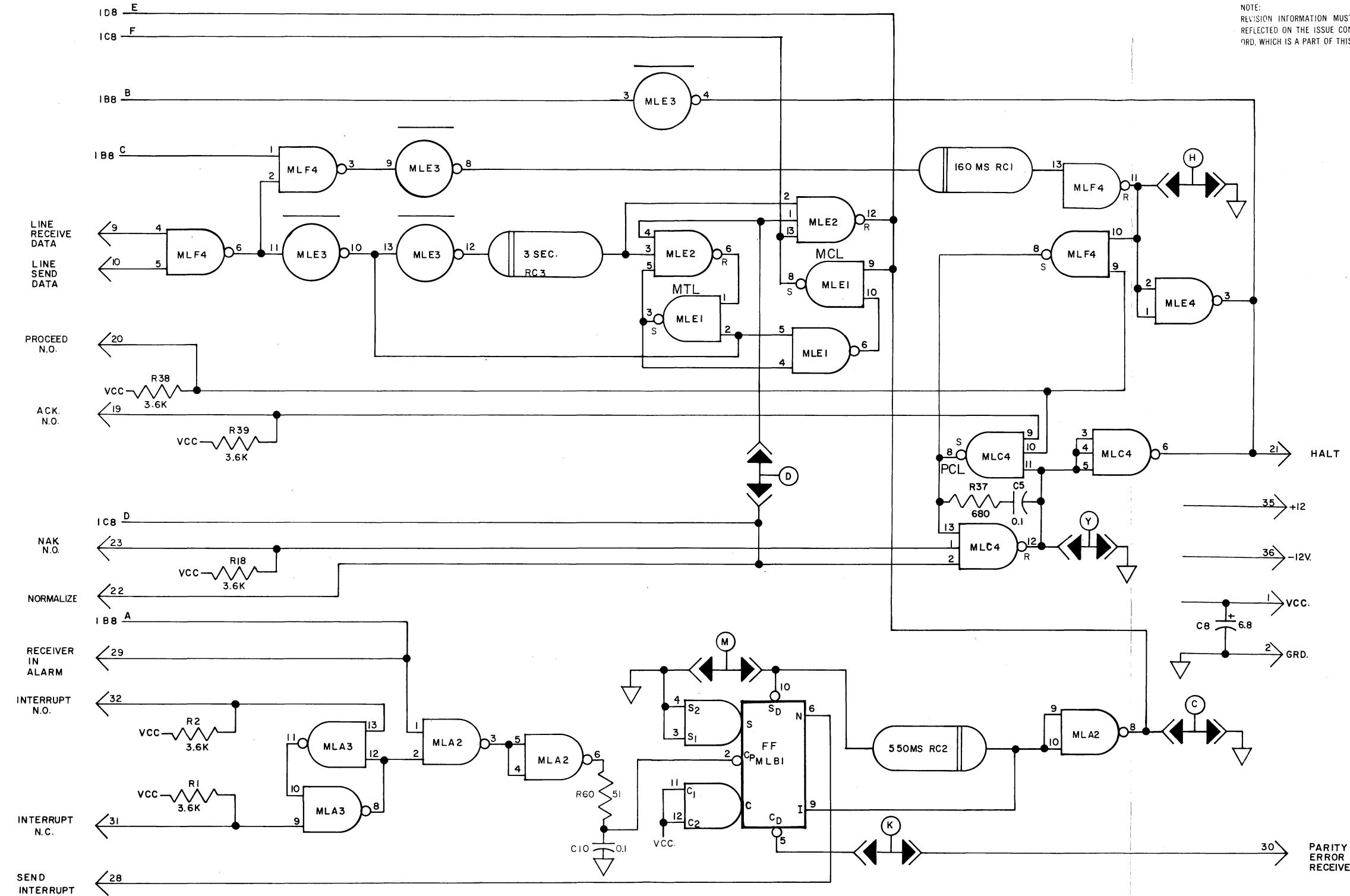

## SECTION II

### DETAILED DESCRIPTION AND THEORY OF OPERATION

#### 1. ASSOCIATED DOCUMENTS

1.1 Schematic Drawing - 8370 WD.

1.2 Assembly Drawing - 303149.

#### 2. DETAILED DESCRIPTION AND THEORY OF OPERATION

##### 2.1 Selector Magnet Driver

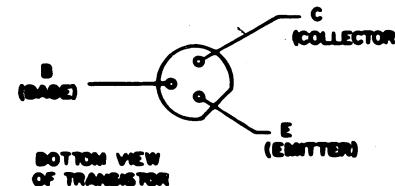

2.1.1 The selector magnet driver circuit is a three stage amplifier, designed to operate full on or off without intermediate levels. The input characteristics are matched to the output of currents sinking DTL integrated circuit elements. The output circuit is matched to the characteristics of the 312936 Selector Magnet Assembly.

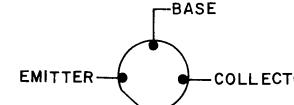

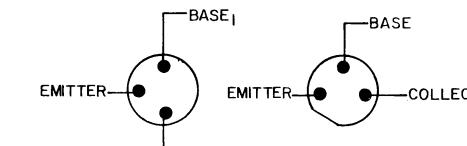

2.1.2 A logic one signal input, (See Section I-2.1), will turn the output on, picking up the selector magnet armature. The logic one signal turns off Q3, allowing Q4 and Q5 to be turned on. With Q5 turned on, C3 will be charged through the load impedance to give a high initial current. As C3 becomes charged, load current will be limited by the external 50 ohm, 50 watt resistor connected across C3.

2.1.3 With a logic zero signal on the input, (see Section I-2.1), Q3 will be turned on, driving the base of Q4 positive, turning off Q4 and Q5. The positive voltage on the base of Q4 is limited by ground clamp Diode CR2. With Q5 turned off, the load inductance and C3 will discharge through steering Diode CR3, and the discharge network C2, R13. The impedance values of the output circuit are chosen to proved equal selector magnet armature pickup and drop-out times. The characteristics of the (loaded) output circuit will determine the maximum signalling rate. The values chosen will give proper operation with a nominal pulse length of 6 ms or more.

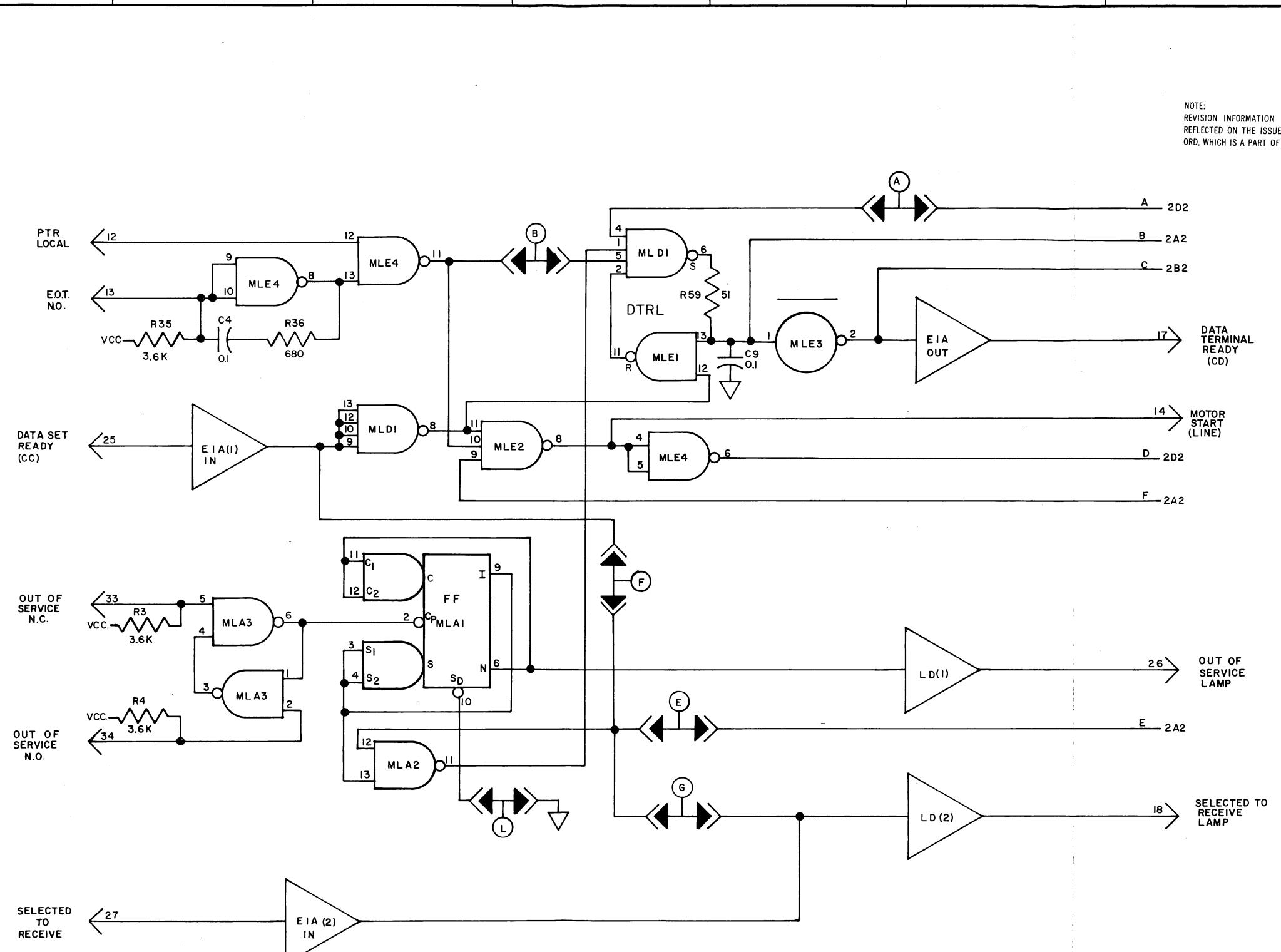

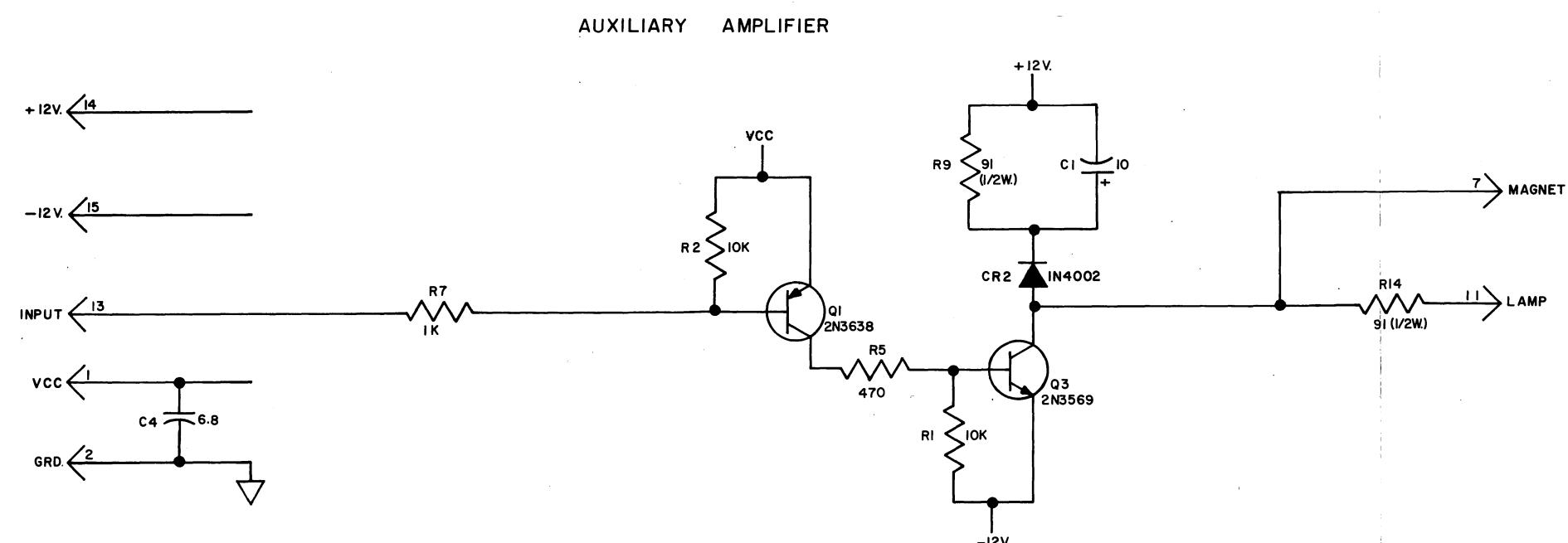

##### 2.2 Motor Control Relay Driver

2.2.1 The motor control relay drive is a two-stage amplifier which is designed to operate full ON or OFF without intermediate levels. This circuit is designed to drive an external motor start relay. Inputs to the motor control relay drive circuit are on Pins 4 and 8. The inputs are connected in a logical OR configuration each having an input resistance of 3.6K. With logic zero, (see Section I-2.1), applied to either input, Q1 is switched ON. This switches Q2 ON, energizing the relay. With logic one applied at both inputs Q1 and Q2 are switched OFF. When Q2 is switched OFF, any positive voltage transient developed by the inductive load will be clamped to the positive supply voltage by CR1.

NOTE: REVISION INFORMATION MUST ALSO BE REFLECTED ON THE ISSUE CONTROL RECORD, WHICH IS A PART OF THIS DRAWING.

SEE ISSUE CONTROL RECORD FOR COMPLETE LIST OF SHEETS COMPRISING THIS W.D.

| NO.                                                                                   | NOTES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |        |                                                                                       |                                                                                       |              |       |                                                                                       |                                                                                       |

|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--------------|-------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| 1.                                                                                    | ALL VOLTAGES DC, UNLESS OTHERWISE SPECIFIED.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |        |                                                                                       |                                                                                       |              |       |                                                                                       |                                                                                       |

| 2.                                                                                    | ALL RESISTORS 1/4 WATT AND RESISTANCE VALUES IN OHMS, UNLESS OTHERWISE SPECIFIED.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |        |                                                                                       |                                                                                       |              |       |                                                                                       |                                                                                       |

| 3.                                                                                    | ALL CAPACITANCE VALUES IN MICROFARADS, UNLESS OTHERWISE SPECIFIED.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |        |                                                                                       |                                                                                       |              |       |                                                                                       |                                                                                       |

| 4.                                                                                    | <br>INDICATES FEMALE CONNECTOR.<br><br>INDICATES MALE CONNECTOR.<br><br><br>INDICATES CIRCUIT GROUND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |        |                                                                                       |                                                                                       |              |       |                                                                                       |                                                                                       |

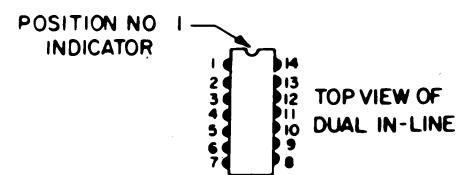

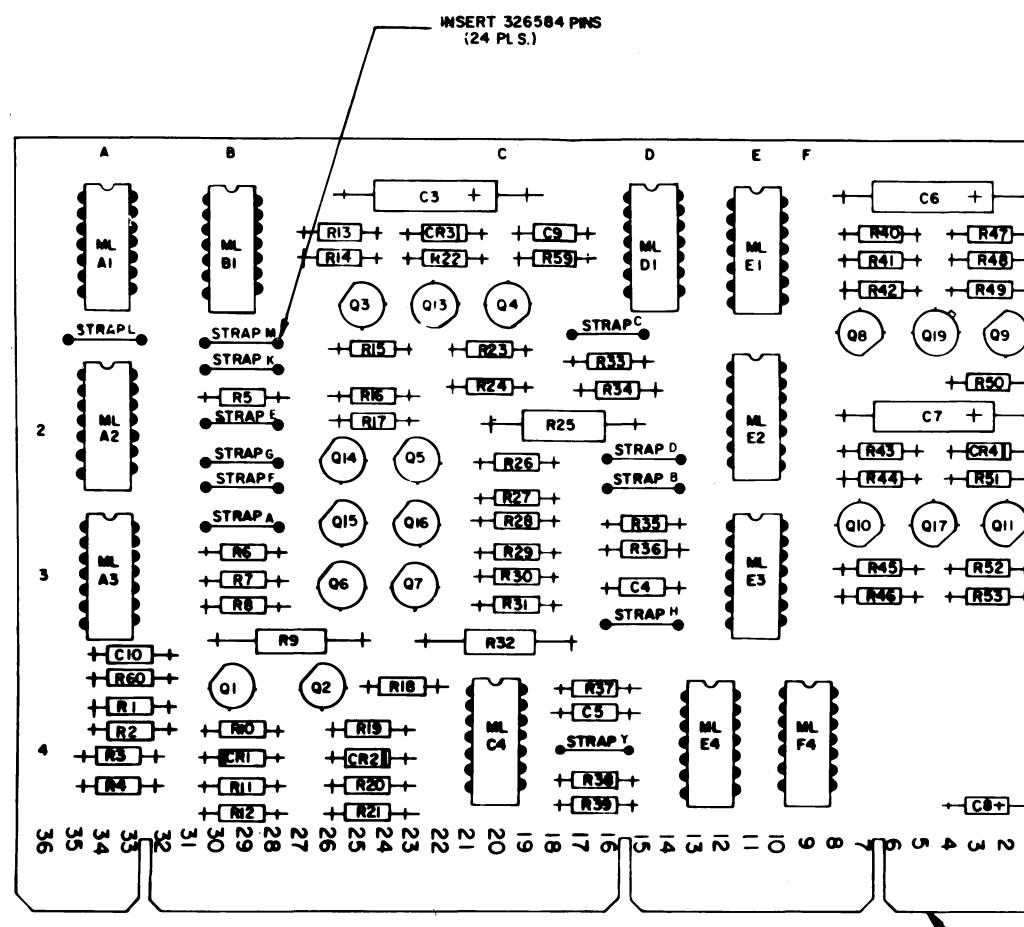

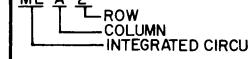

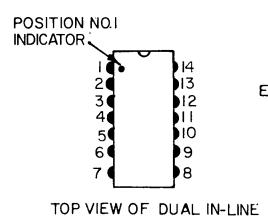

| 5.                                                                                    | <br>ROW<br>COLUMN<br>INTEGRATED CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |        |                                                                                       |                                                                                       |              |       |                                                                                       |                                                                                       |

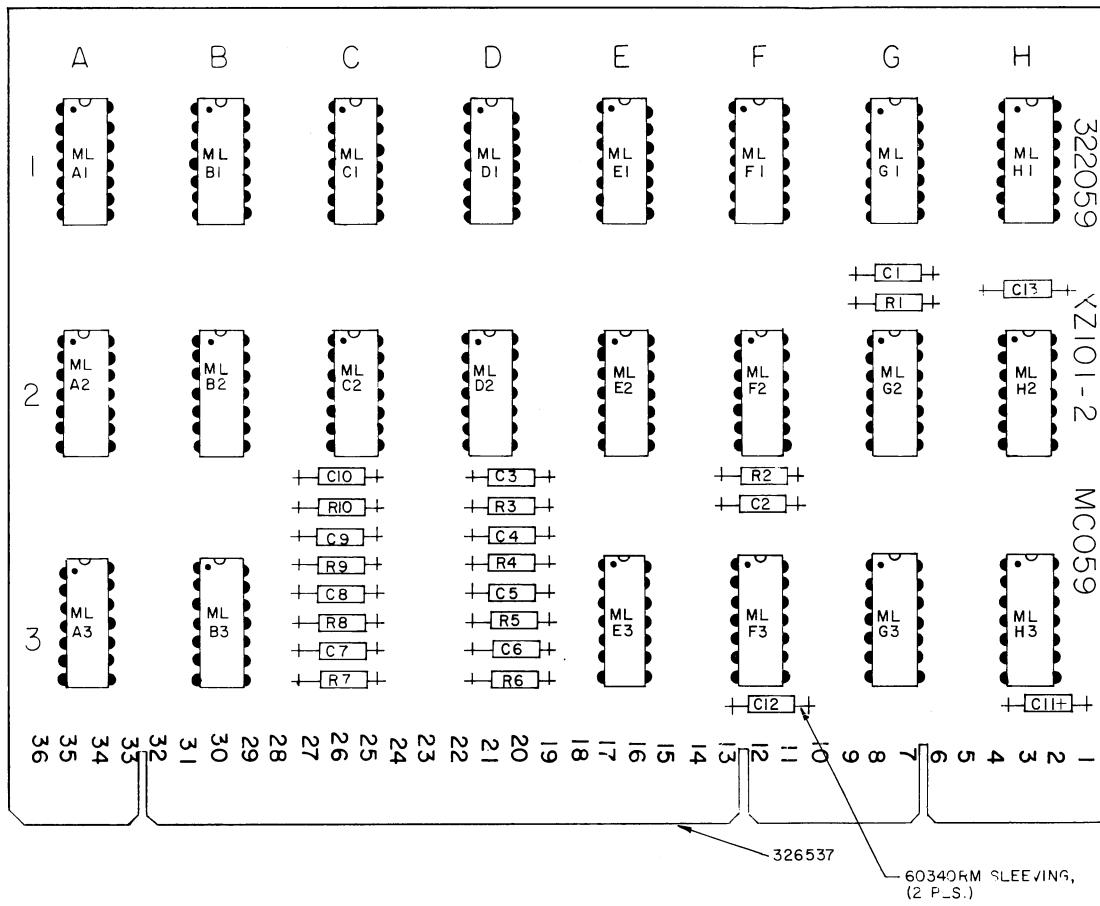

| 6.                                                                                    | ASSOCIATED ASSEMBLY: 322059.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |        |                                                                                       |                                                                                       |              |       |                                                                                       |                                                                                       |