# 3A CENTRAL CONTROL AND CONTROL PANEL FUNCTIONAL DESCRIPTION NO. 2B ELECTRONIC SWITCHING SYSTEM

|    | CONTENTS                           | PAGE | CONTENTS                                                      | ЭE |

|----|------------------------------------|------|---------------------------------------------------------------|----|

| 1. | GENERAL                            | . 4  | 5. FUNCTIONAL DESCRIPTION                                     | 20 |

|    | 3A CENTRAL CONTROL PURPOSE .       | . 4  | 3A CC FUNCTIONAL RELATIONSHIP TO OTHER SYSTEM UNITS           | 20 |

|    | CHARACTERISTICS                    | . 4  | OTHER STREET ONLY                                             | 20 |

|    | BROAD FUNCTIONAL OVERVIEW          | . 5  | A. Communication Functions of 3A CC Within The 2B Processor 2 | 20 |

|    | GENERAL DESCRIPTION OF OPERATION   | . 6  | B. Communication Functions of 3A CC In Relation to Periphery  | 22 |

|    | INTERFACE WITH NO. 2B ESS PERIPHER | _    | 2A CC LOCIC LIMIT                                             | ~~ |

|    |                                    | . 7  | 3A CC LOGIC UNIT                                              | 22 |

| 2. | PHYSICAL DESCRIPTION               | . 8  | A. System Clock                                               | 22 |

|    | 3A CENTRAL CONTROL LOGIC UNIT      | . 8  | B. 3A CC Registers                                            | 27 |

|    | 3A CC CONTROL PANEL                | . 8  | C. Microprogram Control 2                                     | 27 |

| 3. | TECHNOLOGY                         | . 11 | D. Main Memory Control 4                                      | 10 |

|    | BASIC CIRCUITS AND FUNCTIONS .     | . 11 | E. Gating Bus and Bus Parity Checker . 5                      | 50 |

|    | A. Logic Circuits                  | . 11 | F. Data Manipulation Logic 5                                  | 50 |

|    | B. Storage Circuits                | . 12 | G. I/O Channel and Controller 5                               | 56 |

|    | C. R-S Flip-Flop Operation         | . 12 | H. Interrupt Facility 6                                       | 50 |

|    | D. Binary Storage                  | . 12 | I. Maintenance Channel and Maintenance Channel Controller     | 54 |

| 4. | NO. 2B ESS INSTRUCTION SETS        | . 13 |                                                               |    |

|    | 3A INSTRUCTIONS                    | . 13 | J. Control Panel and Control Panel Functions 6                | 57 |

|    | NO. 2B ESS EMULATED INSTRUCTIONS   | . 17 | K. Miscellaneous 6                                            | 8  |

|    | JINIOUE OR INSTRUCTIONS            | . 10 | 4 MICCELLANIEOUS CIDCUITS                                     | ,, |

#### NOTICE

Not for use or disclosure outside the Bell System except under written agreement

|    | CONTENTS                                                  | AGE       | CONTENTS                                                                  | PAGE |

|----|-----------------------------------------------------------|-----------|---------------------------------------------------------------------------|------|

|    | PROTECTION CIRCUITS                                       | 78        | ADD FUNCTION (PR-1C917-01)                                                | 87   |

|    | 3-VOLT REFERENCE AND FILTER CIRCUIT                       | 78        | MATCHER FOR DUPLICATE DML (PR-1C917-01)                                   |      |

| 7. | MAINTENANCE FEATURES                                      | 79        | BOOLEAN LOGIC FUNCTIONS (PR-1C917-01)                                     |      |

|    | FAULT DETECTION                                           | <b>79</b> | FIND LOW ZERO FUNCTION (PR-1C917-01)                                      |      |

|    | MAINTENANCE CHANNEL                                       | 80        |                                                                           |      |

|    | INITIALIZATION                                            | 81        | ROTATE FUNCTION (PR-1C917-01)                                             | 88   |

|    | DOUBLE STORE READ                                         | 81        | PACK AND UNPACK GATING OPERATIONS (PR-1C917-01)                           |      |

|    | COMPLEMENT CORRECTION                                     | 81        | MICROCONTROL PART 1 (PR-1C919-01) .                                       | 89   |

|    | CONTROL PANEL                                             | 82        | MICROCONTROL PART 2 (PR-1C919-A1) .                                       | 89   |

| 8. | DIAGNOSTICS                                               | 82        | MICROCONTROL PART 3 (PR-1C919-B1) .                                       |      |

|    | MAINTENANCE CHANNEL (PR-1C912-01)                         | 85        | MICROCONTROL PART 4 (PR-1C919-C1) .                                       |      |

|    | GATING BUS (PR-1C912-01)                                  | 85        | DS FLIP-FLOP (PR-1C920-01)                                                | 91   |

|    | CLOCK (PR-1C912-01)                                       | 85        | ADDRESS INCREMENT ADDER (PR-1C920-01)                                     |      |

|    | VERIFICATION OF INITIALIZATION BY MONITOR (PR-1C912-01)   | 85        | STORE BUS CONTROLLER PART 1 (PR-1C921-01)                                 |      |

|    | "TO" DECODER (PR-1C913-01)                                | 86        | STORE BUS CONTROLLER PART 2                                               |      |

|    | "FROM" DECODER (PR-1C913-A1)                              | 86        | (PR-1C921-01)                                                             |      |

|    | TEST FOR MULTIPLE FIRING "FROM" CROSSPOINTS (PR-1C914-01) | 86        | MICROINTERPRET OPERATION (PR-1C930-01)                                    |      |

|    | TEST FOR MULTIPLE FIRING "TO" CROSSPOINTS (PR-1C914-01)   | 86        | TEST FOR MULTIPLE FIRING MISCELLANEOUS CROSSPOINTS (PR-1C930-01)          |      |

|    | GENERAL REGISTERS GATING (PR-1C915-01)                    | 86        | GATING BUS PARITY CHECKER (PR-1C930-01)                                   |      |

|    | SPECIAL REGISTER GATING (PR-1C915-A1)                     | 86        | IB REGISTER X AND Y FIELD PARITY GENERATOR AND PARITY CHECK (PR-1C930-01) |      |

|    | MICROSTORE CONTENT (PR-1C916-01) .                        | 87        | PROGRAM TIMER AND TIMING COUNTER                                          |      |

|    | FUNCTION REGISTER (PR-1C917-01)                           | 87        |                                                                           | 94   |

|     |      | CONTENTS                                                           | PAGE | CONTENTS                                                                                                  | PAGE |

|-----|------|--------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------|------|

|     | INI  | TERRUPTS (PR-1C931-01)                                             | 94   | FIGURES                                                                                                   |      |

|     | PAI  | NEL ADDRESS MATCHER (PR-1C931-01)                                  | 95   |                                                                                                           |      |

|     | PA   | NEL DATA MATCHER (PR-1C931-01)                                     | 95   | 1. 3A Central Control                                                                                     | . 6  |

|     | I/C  | CHANNELS (PR-1C931-01)                                             | 95   | 2. Block Diagram of No. 2B ESS                                                                            | . 7  |

|     |      | ATUS BITS AND INITILIZATION                                        |      | 3. Block Diagram of 3A CC                                                                                 | . 9  |

|     | •    | R-1C932-01)                                                        | 96   | 4. Block Diagram of 2B Processor Illustrating 3A CC I/O Subchannel Interface                              | . 11 |

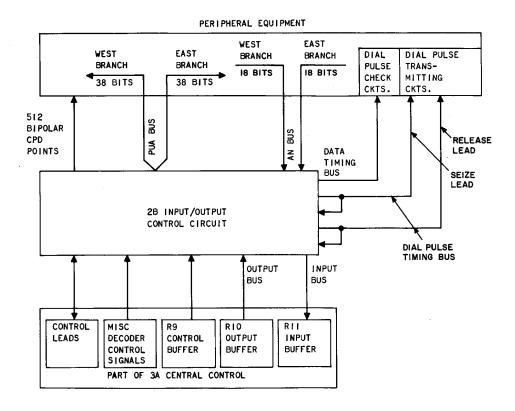

|     |      | ATUS BITS AND TIME-OUTS (PR-1C932-01)                              | ~/   | 5. 2B I/O Control Circuit Bus Connections                                                                 | . 12 |

|     | DO   | UBLE STORE READ (PR-1C911-01)                                      | 97   | 6. 2B Processor Frame                                                                                     | . 13 |

| 9.  | GL   | OSSARY                                                             | 97   | 7. Cabling and Connectors                                                                                 | . 14 |

|     |      |                                                                    |      | 8. 3A CC Circuit Pack Locations                                                                           | . 15 |

|     |      |                                                                    |      | 9. FA-Type Circuit Pack                                                                                   | . 17 |

|     |      |                                                                    |      | 10. FC-Type Circuit Pack                                                                                  | . 18 |

| TAB | LES  |                                                                    |      | 11. Nand Circuit                                                                                          | . 19 |

|     | A.   | STATE AND USE OF THE TWO CONTROL BITS IN MICROINSTRUCTION REGISTER |      | 12. Example of Logic Circuit                                                                              | . 19 |

|     |      |                                                                    | 29   | 13. Basic Flip-Flop Circuit                                                                               | . 19 |

|     | B.   | FUNCTION OF MICROCONTROL STATUS REGISTER BITS                      | 37   | 14. 3A Instructions                                                                                       | . 19 |

|     | C.   | DESIGNATIONS AND FUNCTIONS OF                                      |      | 15. General Format of 3A Instruction Set .                                                                | . 20 |

|     |      | MAIN MEMORY STATUS REGISTER                                        | 49   | 16. Unique 2B Instructions and No. 2B Emulated Instructions                                               |      |

|     | D.   | DEFINED LEVELS AND BIT LOCATIONS IN THE INTERRUPT SET REGISTER     | 64   | 17. Mapping of Two Half Word Instructions Into a 26-Bit Store Word                                        |      |

|     | E.   | 3A CC CONTROL PANEL KEYS, LAMPS, AND SWITCHES                      |      | <ol> <li>Mapping of a Full Word Instruction With<br/>a 16-Bit Address Into a 26-Bit Store Word</li> </ol> |      |

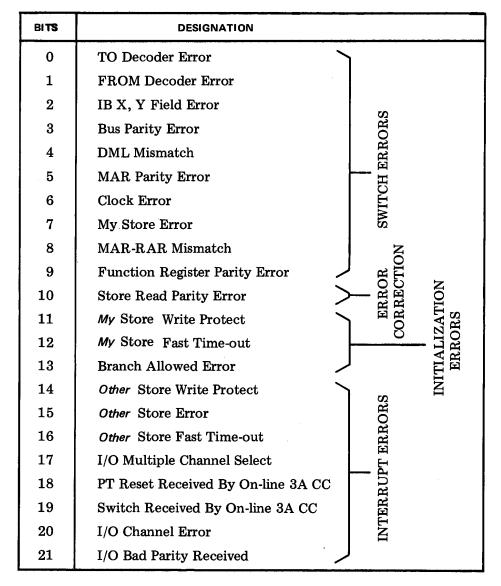

|     | F.   | INDICATIONS OF ERROR REGISTER                                      | 75   | · · · · · · · · · · · · · · · · · · ·                                                                     |      |

|     | G.   | DESIGNATIONS AND FUNCTIONS OF BITS IN SYSTEM STATUS REGISTER       | 77   | 19. Maintenance Channel Interconnections .                                                                | . 22 |

|     | Н.   | FUNCTION OF MAINTENANCE STATE                                      |      | 20. Functional Schematic of 3A CC                                                                         | . 23 |

|     | - •• | REGISTER BITS                                                      |      | 21. Clock Pulse Waveforms                                                                                 | 25   |

|     | I.   | DIAGNOSTIC TEST SEQUENCE OF 2B PROCESSOR                           |      | 22. Prescaler, Timing Counter, and Program Timer                                                          |      |

|             | CONTENTS                                           | PAGE              | 1. GENERAL                                                                                            |

|-------------|----------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------|

| 23.         | 2-Bit Register Cell                                | . 28              | 1.01 This section provides a functional description of the 3A Central Control (3A CC) and the         |

| 24.         | Layout of General Registers                        | . 28              | 3A CC control panel. The 3A CC contains all the necessary logic required to direct and control the    |

| 25.         | Microprogram Control Block Diagram                 | . 30              | processing and handling of data within the No. 2B Electronic Switching System (ESS).                  |

| 26.         | Loading of Microaddress Register                   | . 31              | 3A CENTRAL CONTROL PURPOSE                                                                            |

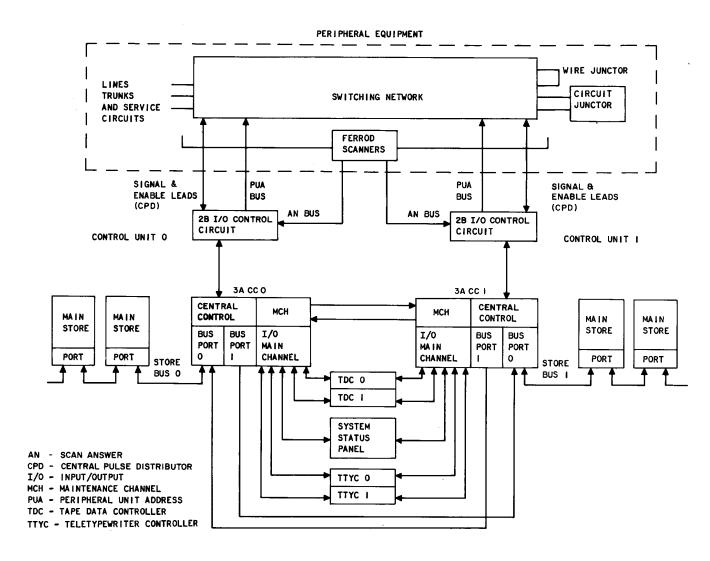

| <b>27</b> . | Normal Microinstruction Execution .                | . 33              | 1.02 The 3A CC (Fig. 1) is an 18-bit (16 data                                                         |

| 28.         | Normal Operand Translation                         | . 34              | bits and 2 parity bits) switching central control designed for electronic switching systems.          |

| 29.         | Swap Operand Translation                           | . 35 <sup>°</sup> | The 3A CC is used in a duplex system configuration in the No. 2B ESS. The duplex configuration        |

| 30.         | Address and Control Parity Checking                | . 36              | (Fig. 2) involves the duplication of system components for continuous real-time operation with a high |

| 31.         | Microsubroutine Return                             | . 39              | degree of system reliability. One 3A CC always has active control over the system while the other     |

| 32.         | Conditional Transfers                              | . 41              | 3A CC operates in a standby mode. A 3A CC, the associated memory, the 2B input/output control         |

| 33.         | Microstore Indexing                                | . 43              | circuit, and processor frame power unit form a control unit (CU) which is a single switchable entity. |

| 34.         | Microaddress Register-Return Address Register      |                   | Therefore, each CU is a separate and complete                                                         |

|             | Matching                                           | . 45              | unit capable of controlling the peripherals and system actions. The on-line 3A CC keeps both          |

| 35.         | Main Memory Control                                | . 47              | the on-line and off-line memory up-to-date so that<br>the standby 3A CC can assume control of the     |

| 36.         | Main Memory Control-Microprogram Control Interface | l<br>. 51         | system as required.                                                                                   |

| 37.         | Flow of 3A and 2B Instructions                     | . 53              | CHARACTERICS                                                                                          |

| ٠,٠         |                                                    |                   | 1.03 The major characteristics of the 3A CC are:                                                      |

| 38.         | Load New OP Code Operation                         | . 54              | • 1A Technology: This technology, which                                                               |

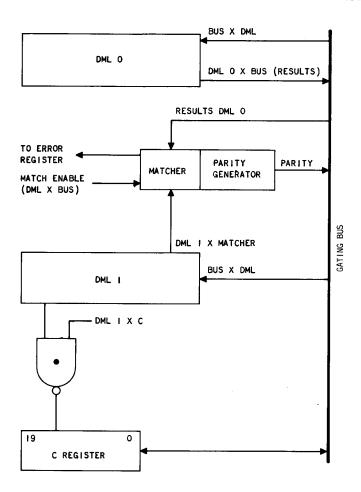

| 39.         | Duplicated Data Manipulation Logic .               | . 55              | provides standardized logic gates implemented with silicon intergated circuits (SICs) mounted         |

| 40.         | Breakdown of Data Manipulation Logic               | . 57              | on ceramics which use automated packaging<br>and interconnections techniques, enables the             |

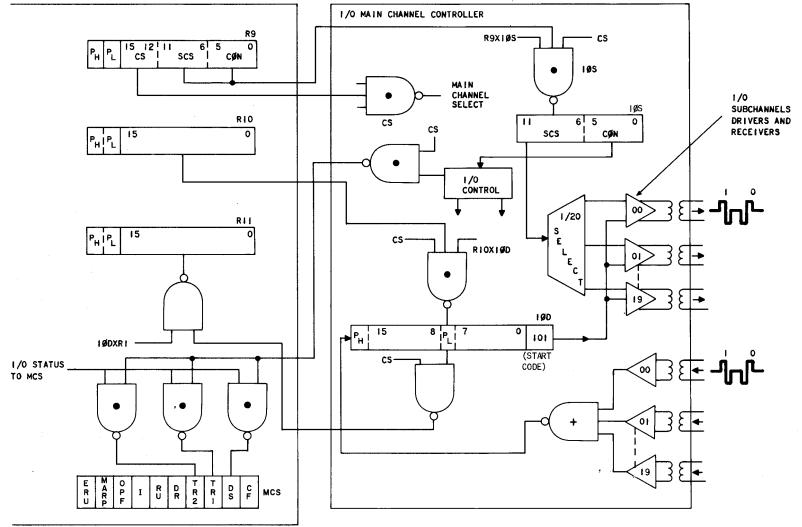

| 41.         | Input/Output Facility                              | . 59              | 3A CC to be small in size, economical in price, and to function at a very fast speed                  |

| 42.         | Input/Output Main Channel Controller               | . 61              | when compared to the CCs of earlier ESS systems.                                                      |

| 43.         | Interrupt Facility                                 | . 63              | • Self-Checking Circuits: The 3A CC                                                                   |

| 44.         | Maintenance Channel Controller                     | . 65              | uses self-checking circuits to give immediate detection of faults. These circuits eliminate           |

| <b>45</b> . | Registers Associated With Control Panel Operations |                   | the process of synchronous operation and<br>match comparison between two control units                |

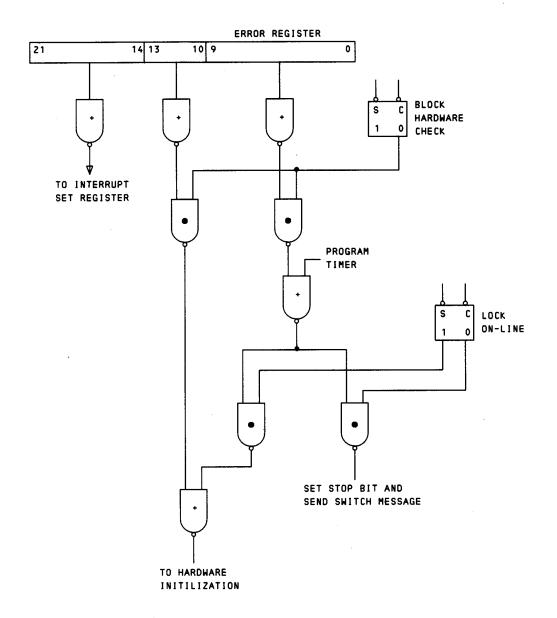

| 46.         | Error Register and Associated Circuitry            | . 76              | while still providing rapid detection of failures.                                                    |

- Microprogram Control: The internal sequencing of actions is controlled by a microprogram structure which results in a highly flexible means of implementing the instruction set and basic control functions. Each instruction is performed by a sequence of microinstructons within the microprogram control. The microcycle time (time to perform one microinstructon) is 150 nanoseconds.

- Asynchronous Communication to Memory and the Periphery: Additional flexibility is allowed by the asynchronous nature of both the 3A CC-to-memory and 3A CC-to-periphery communication. This means that after ordering the memory or periphery to accomplish a task, the 3A CC can proceed to other tasks without having to further control those units in their performance. At a later time, the 3A CC returns for the memory or peripheral response.

- Flexible Input/Output (I/O) Communication: A modular, loosely coupled, I/O structure provides the capability of handling a wide variety of I/O devices. This I/O facility is growable by increments of 20 subchannels up to a maximum of 360 high-speed (6.67 megabits per second) serial I/O subchannels.

- Large Addressing Capability: The 3A CC may directly access up to 1,048,576 words of storage by using a 20 bit address.

- Sixteen General Registers: General purpose registers in the 3A CC provide flexibility in data handling and processing.

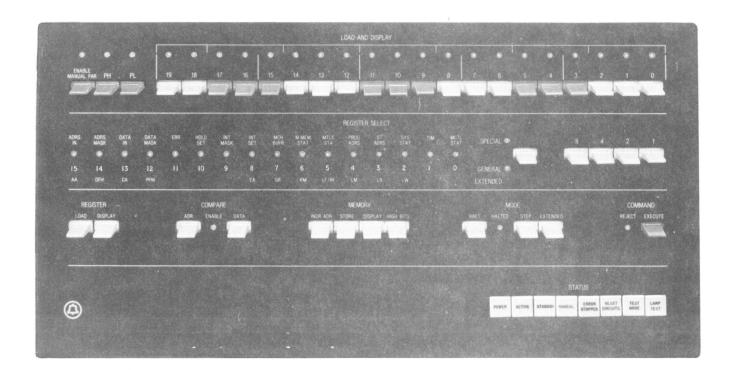

- Manual Control and Display Panel: The 3A CC has a control panel by which maintenance personnel can gain access to the unit for testing or performing manual operations.

#### **BROAD FUNCTIONAL OVERVIEW**

ţ

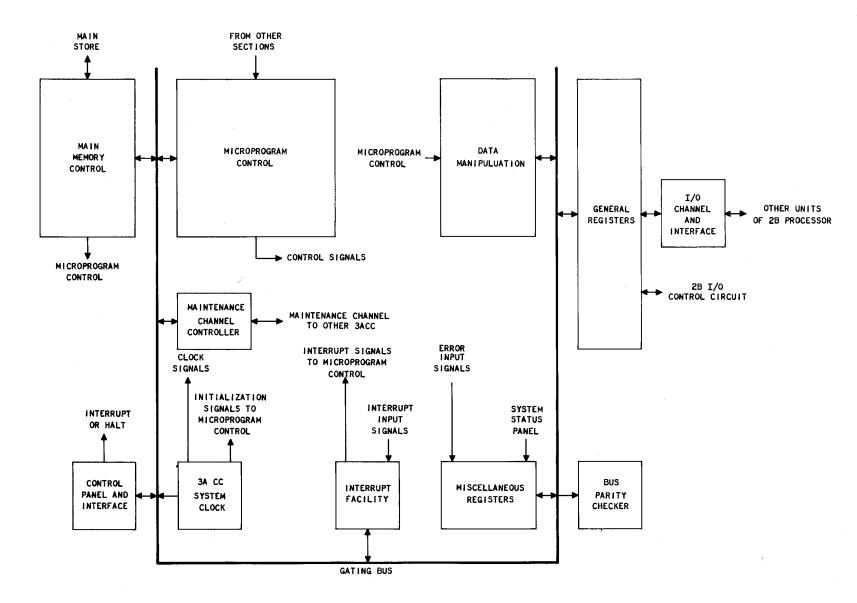

- 1.04 A block diagram in Fig. 3 shows the functional sections within the 3A CC. The functional sections are:

- Microprogram Control: The microprogram control is the heart of the 3A CC operation. It directs and controls the operation of the

- other functional sections within the 3A CC. Since the internal sequencing of actions is controlled by a microprogram structure, a highly flexible means of implementing the instruction set as well as control functions is provided. Each main memory or control function instruction is performed by a sequence of microinstructions executed by the microprogram control. Each microinstruction performs an elementary function such as gating between two registers, loading the data manipulation logic or activating a control The proper sequencing of these elemental functions results in the execution of a main memory instruction (i.e., macroinstruction) or one of the control functions required by the 3A CC operation (i.e., initialization).

- **System Clock:** The system clock supplies the basic timing pulses necessary to control system actions.

- General Registers: The general registers provide a quick access storage medium for storing data being used in the current data processing operation.

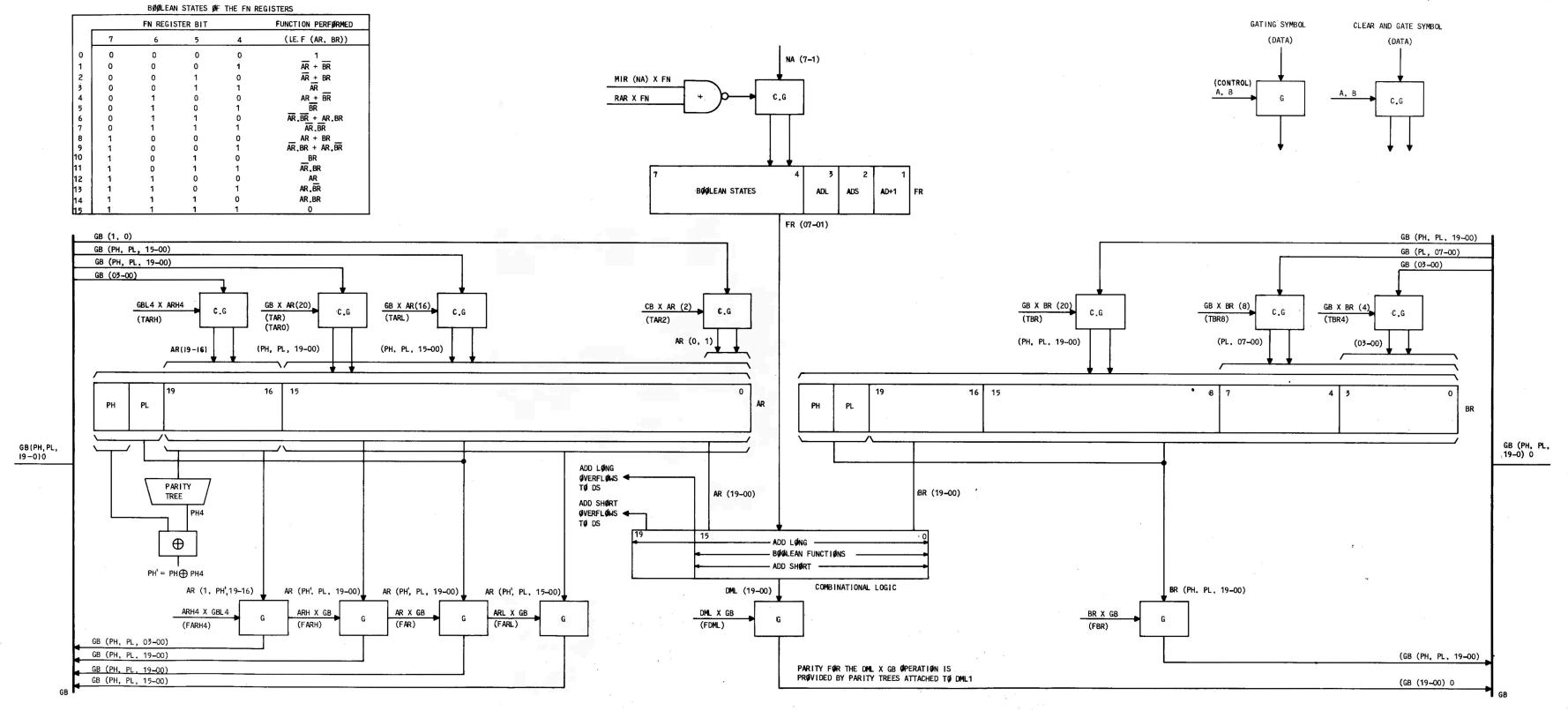

- Data Manipulation: The data manipulation section performs all arithmetic and logic operations upon one or two operands.

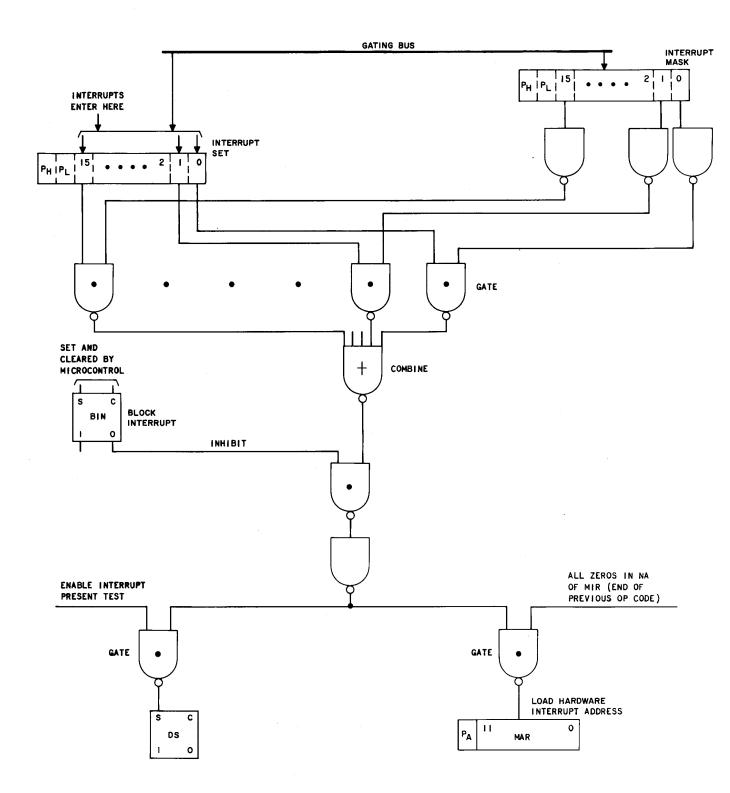

- Interrupt Facility: The interrupt facility provides the means of interrupting the program flow so that a timed or a demanded task may be performed.

- Main Memory Control: The interface by which information is transmitted to or received from the main store.

- I/O Channel and Controller: The interface by which information is transmitted to or received from the other units of the 2B processor.

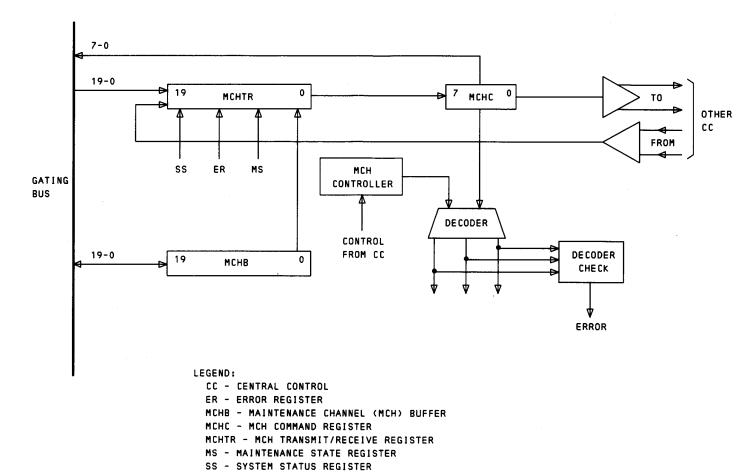

- Maintenance Channel and Controller: The maintenance channel and controller provide the means by which information is transmitted between the duplicated 3A CCs for maintenance purposes.

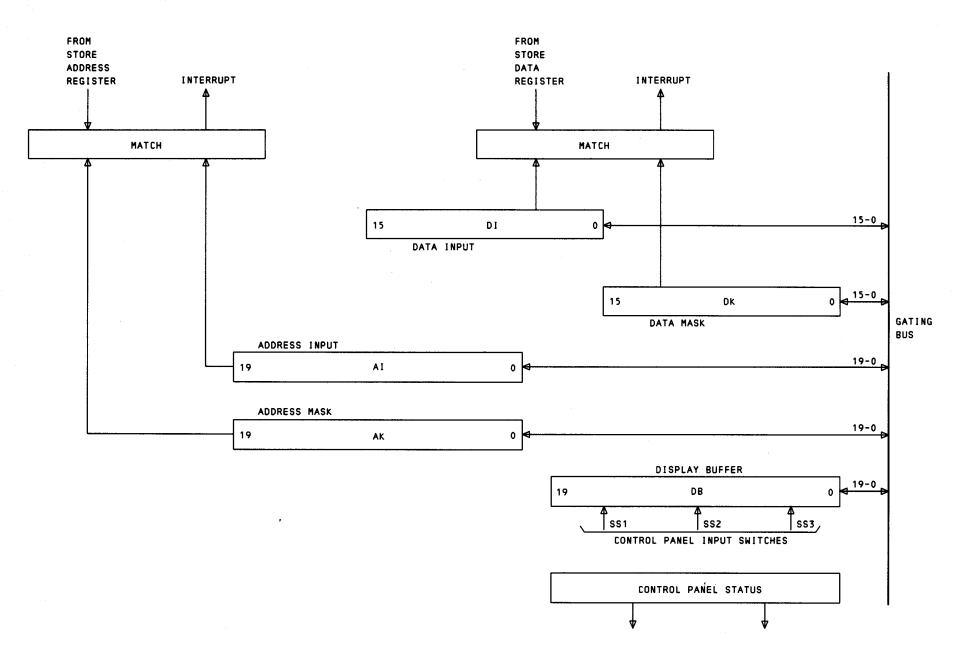

- Control Panel and Interface: The control panel provides one of the means of

communication between the 3A CC and the maintenance personnel.

- Gating Bus and Bus Parity Checker: The gating bus is the communications path within the 3A CC. The bus parity checker tests the parity of the information placed on the gating bus to ensure its accuracy.

- Miscellaneous: This section contains a group of special registers and cable receivers. The cable receivers provide a means for receiving information from the system status panel. The special registers are buffers mainly for maintenance, control, status, and error information.

#### GENERAL DESCRIPTION OF OPERATION

1.05 The 3A CC comprises a large number of registers and their associated control logic circuitry. The 3A CC requests a sequence of commands from the main store (MAS) and translates them into action. This action usually results in the movement of data between the registers in the 3A CC or between the register in the 3A CC and the MAS. The MAS instruction points to the

starting address in the microstore of a sequence of microinstruction that will cause the microprogram control to perform a required action. The first microinstruction of an instruction sequence is also typically used to issue a control function to request the next word to be accessed from the MAS. The action is performed by a sequence of microinstruction steps. The initiation of a microinstruction sequence consists of reading a word out of the MAS. This word indicates the location of the first microinstruction to be performed as well as the address of the next microinstruction to be performed.

1.06 At the completion of the sequence of microinstructions, the microprogram control interrogates the data ready flip flop to determine whether the fetch for the next instruction has been completed from the MAS. If not, the microprogram control goes into a loop in which it constantly checks to see if the MAS cycle is complete. When the MAS cycle is complete, the next instruction is loaded into the 3A CC and a new microinstruction sequence is initiated.

1.07 The 3A CC also has the ability to write into MAS. Writing is normally performed in the temporary storage portion of the MAS. The

Fig. 1-3A Central Control

Fig. 2-Block Diagram of No. 2B ESS

other portions of the MAS are write-protected and an ordered sequence of operations is required to allow the 3A CC to write into protected areas of the MAS.

# INTERFACE WITH NO. 2B ESS PERIPHERY

- 1.08 The 3A CC accesses and controls the No. 2B ESS periphery through the 3A CC input/output (I/O) main channel and the 2B I/O control circuit, which is a part of the 2B processor.

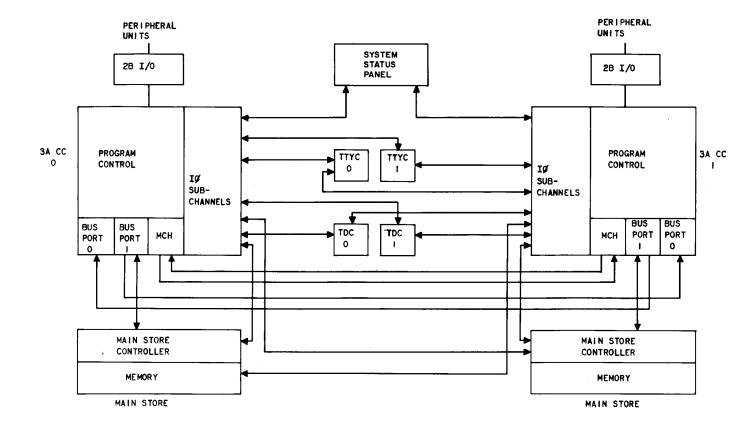

- 1.09 The I/O main channel (see Fig. 2) is one means by which information is transmitted to or received from the other units of the 2B processor. The I/O main channel provides serial

AC data at 6.67 mega bits per second and has a 20-subchannel capacity. An I/O subchannel is provided to each main store controller (MASC), tape data controller (TDC), teletypewriter (TTY) controller and system status panel (SSP) (Fig. 4).

1.10 The 2B I/O control circuit performs the interfacing function between the 3A CC and the relatively low-speed peripheral equipment (Fig. 5). The 2B I/O control circuit is the buffer circuit through which inputs are received into the processor and from which outputs are transmitted to the peripheral equipment. Refer to Sections 232-309-101 2B Processor Description, and 232-309-108, Functional Description of 2B I/O Control Circuit,

for more information on the interface functions of the 2B I/O control circuit.

#### 2. PHYSICAL DESCRIPTION

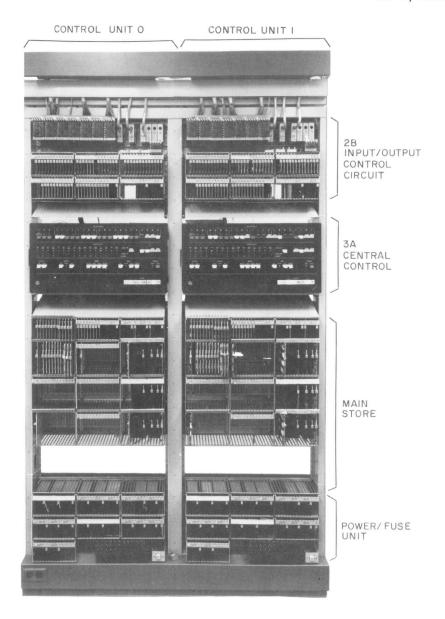

- 2.01 The 3A CC is located in the upper midsection of each bay of the processor frame (Fig. 6). The position on the frame provides the operator convenient access to the keys and switches of the 3A CC control panel. The 3A CC is 23-1/2 inches wide, 12 inches high, and approximately 14 inches deep. Basically, the 3A CC consists of the logic unit and the control panel.

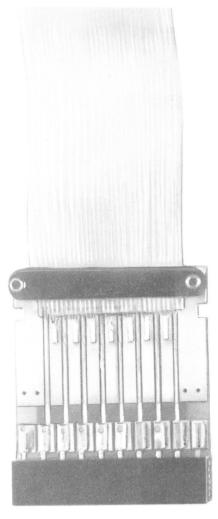

- 2.02 All interconnections between the 3A CC and other units are accomplished by one of the following types of cabling techniques (Fig. 7). The first type of cable is a 30-gauge 31-conductor, flat ribbon cable; the second consists of coaxial cable. Both types of cable require a connector and paddleboard assembly at each end. Coaxial cable with a subminiature RF-type connector may also be used in the interconnection of certain units.

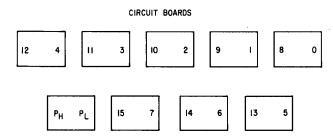

# 3A CENTRAL CONTROL LOGIC UNIT

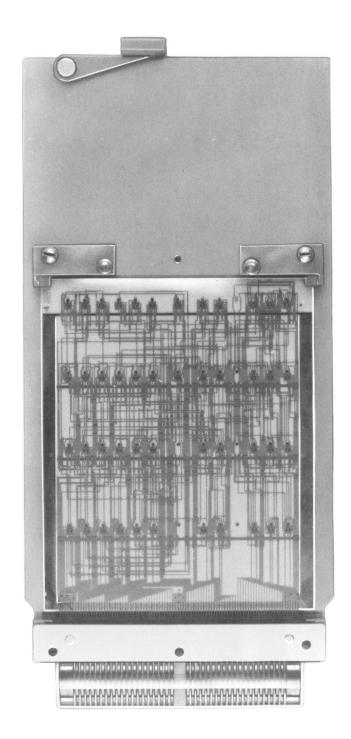

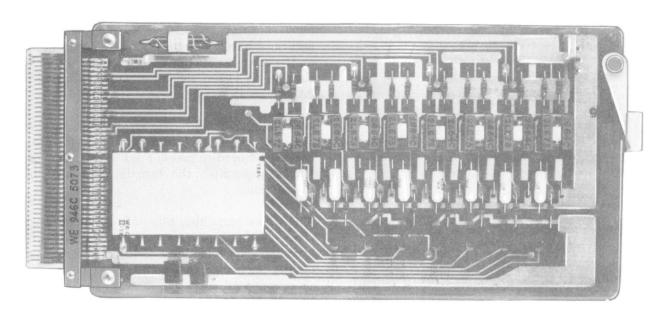

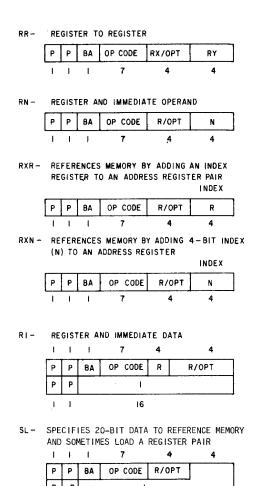

- 2.03 A 12-inch mounting plate provides the necessary structure for mounting eight 80A apparatus housings. These housings hold the 3A CC logic unit circuit packs. The 3A CC uses four types of 1A circuit packs (FA, FB, FC, and ED types). Figure 8 shows the arrangement of the circuit packs in the 3A CC.

- 2.04 The FA-type circuit packs (Fig. 9) may contain a maximum of 52 silicon integrated circuit (SIC) chips mounted on a ceramic substrate which is approximately 3-1/4 by 4 inches in size. The ceramic substrate is mounted on a removable circut board (4 by 7-3/4 inches) with an 82-pin connector. In the 3A CC there are 54 FA-type circuit packs with an average of 43 SIC chips on each (300 gates) for a total of approximately 16,000 gates in the 3A CC.

- 2.05 The FB- and FC-type (Fig. 10) circuit packs are very similar to each other. Both types contain discrete devices and may contain hybrid integrated circuits (HICs). A HIC is a integrated circuit consisting of SICS or other chip components and thin film devices bonded to a ceramic substrate. The major difference between the FB- and FC-type packs is their means of external connections. The

FB-type circuit packs use a 42-pin connector; the FC-type pack uses an 82-pin connector.

2.06 The microprogram store of the 3A CC consists of ED-type circuit packs which are very similar to the FC-type circuit packs. The ED-type circuit packs contain eight programmable read-only memory (PROM) devices, seven T<sub>2</sub>L interfacing devices, and pull-up resistors. The PROM devices are 1K dual in-line packages (DIPs) arranged with 265 words by four bits. The ED-type circuit packs use 82-pin connectors.

# **3A CC CONTROL PANEL**

- 2.07 The control panel consists of a 12-inch by 23-1/2 inch aluminum panel, silk-screened black with the appropriate nomenclature. The panel includes the following apparatus:

- (a) Status indicator lamps and switches

- (b) Light-emitting diodes (LEDs) which display register contents or main memory address or data information

- (c) Register select switches for loading or displaying purposes

- (d) Switches for selecting a particular manual function.

- 2.08 The panel is mounted to an aluminum frame and has a printed wiring board which supports all the apparatus and circuitry necessary for the control panel to function. The entire assembly is hinged to the side brackets of the 3A CC logic unit to provide access to the circuit packs within the unit. Most of the interconnections between the panel and the rest of the 3A CC are accomplished by means of a connectorized flat tape cable assembly. Some interconnections are by the coaxial cable type.

- 2.09 The panel is subdivided into the following areas:

- (a) LOAD AND DISPLAY

- (b) REGISTER SELECT

- (c) REGISTER

- (d) COMPARE

Fig. 3—Block Diagram of 3A CC

Fig. 4—Block Diagram of 2B Processor Illustrating 3A CC I/O Subchannel Interface

- (e) MEMORY

- (f) MODE

- (g) COMMAND

- (h) STATUS

The keys, lamps, and switches of these areas and their purpose are covered in detail in part 5.

### 3. TECHNOLOGY

#### **BASIC CIRCUITS AND FUNCTIONS**

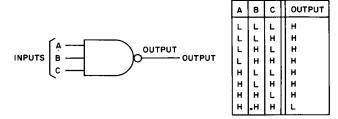

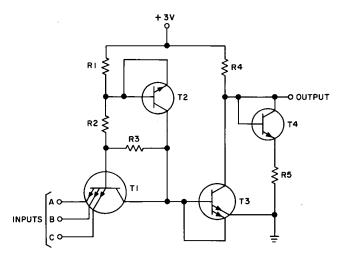

3.01 The 3A CC performs logic and memory functions. Its basic building block is the NOT-AND (NAND) circuit (Fig. 11A) which is used as a gate for logic functions and is combined into flip-flops for memory functions. The output of the NAND gate is low only when all its inputs are high; its output is high whenever any one of its inputs is low. The NAND gate is implemented

with a transistor-transistor logic gate (T<sub>2</sub>L) as shown in Fig. 11B.

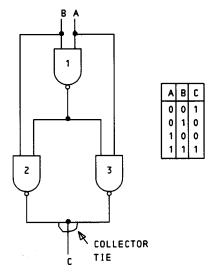

# A. Logic Circuits

3.02 A circuit performs a logic function if it generates an output when certain specified input conditions exist. Examples of logic circuits are a single NAND used as a gate and a combination of NAND gates that provide a specified output only when specific input conditions exist. As shown in Fig. 12, NAND gates are combined to meet a specified condition. This circuit also utilizes a collector tie which performs an additional logic function without the use of any additional gates. The collector tie functions as an AND gate and is an attribute of 1A logic. The NAND gates and collector tie are combined to produce a high output at C only when inputs A and B are both high or both low.

Fig. 5—2B I/O Control Circuit Bus Connections

# **B. Storage Circuits**

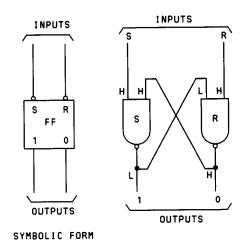

3.03 A circuit which is stable in either of two states can perform a storage function and can remain in the state selected. The basic 3A CC storage circuit is a R-S flip-flop which consists of two NAND gates connected so that the output of each gate is an input to the other gate (Fig. 13). This flip-flop has two inputs, set (S) and reset (R), and two outputs, 1-side (1) and O-side (O). It can acquire and retain either of two states, set or clear, in response to a momentary low signal on input S or R, respectively.

#### C. R-S Flip-Flop Operation

3.04 Assume that inputs S and R are both high and that the circuit is in the clear state (output 0 high and output 1 low). Since both inputs of the S gate are high, its output is low.

This, in turn, keeps one of the inputs of the R gate low and insures that its output is high. Thus, the flip-flop is stable in the clear state.

3.05 If the S input is pulsed low, the output of the S gate goes high. This high is applied to one input of the R gate, and since both of its inputs are now high, the output of the R gate goes low. Since the low output of the R gate is fed back to the input of the S gate, it insures that the output of the latter stays high even when the S input goes high again. Thus, the flip-flop is now stable in the set state and will remain in this state until the R input goes low.

#### D. Binary Storage

3.06 In order to store a binary 1, a flip-flop is set by the application of a low voltage (binary 0) to its S input. Therefore, its 1-side

Fig. 6—2B Processor Frame

output is high (H), and its 0-side output is low (L). Similarly, to store a binary 0, a flip-flop is cleared by the application of a low voltage to its C input; its 1-side output is low, and its 0-side output is high.

#### 4. NO. 2B ESS INSTRUCTION SETS

- **4.01** The No. 2B ESS utilizes two basic instruction sets:

- 3A instruction set

- 2B instruction set

The 3A instructions are used to control the internal sequencing, diagnostics and maintenance of the 3A CC. The 2B instructions are used for the execution

of call processing programs, peripheral unit diagnostic and maintenance programs, and unique 2B programs. The 2B instruction set consists of new 2B instructions and approximately 75 percent of the No. 2 ESS instructions. The new 2B instructions are combined with both the No. 2 and 3A instructions for the unique 2B programs.

## **3A INSTRUCTIONS**

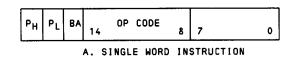

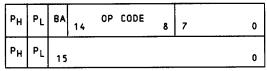

4.02 The 3A instructions consist of single (full) word instructions and double word instructions(Fig. 14). Single word instructions are the most commonly used; however, double word instructions are used when either 16 bits of data or a 20-bit address is required in an instruction.

31-CONDUCTOR RIBBON CABLE AND PADDLEBOARD CONNECTOR

COAXIAL CABLES AND PADDLEBOARD CONNECTOR

Fig. 7—Cabling and Connectors

- 4.03 The 3A CC instructions are general purpose in nature to enable reading from or writing into any of the general registers. Since most of the instructions allow any general register to be used, it is not necessary to move the data to a special register to perform a function.

- **4.04** The general formats (Fig. 15) for the 3A CC instruction are:

- RR Register to Register

- RN Immediate Operand to Register

- RXR References memory by adding an index register to an address register

- RXN References memory by adding N to an address register pair

- RI Register and Immediate Data

- SL—Specified 20-bit data to reference memory and sometimes load a register pair.

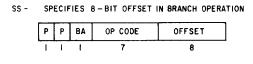

- SS Specified 8-bit OFFSET in branch operation

All are single word type instructions except RI and SL. Each instruction format contains two parity bits, one branch allowed (BA) bit, and a 7-bit operation (OP) code.

| Г |               | •                                          | I,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | /O CHAP                 | INEL #C            | 00                               | `               |                 |                 |          |                 |               |                  |                  |                  |                                        |                                                       |                                              |                    |                                             |                              |                               |                                  |                               |                    |                            |                            |                                                             |                    |                  |                  |                              |                            |                  |                   |                   |    |                  |                  |                      |                      |                      |                 |

|---|---------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------|----------------------------------|-----------------|-----------------|-----------------|----------|-----------------|---------------|------------------|------------------|------------------|----------------------------------------|-------------------------------------------------------|----------------------------------------------|--------------------|---------------------------------------------|------------------------------|-------------------------------|----------------------------------|-------------------------------|--------------------|----------------------------|----------------------------|-------------------------------------------------------------|--------------------|------------------|------------------|------------------------------|----------------------------|------------------|-------------------|-------------------|----|------------------|------------------|----------------------|----------------------|----------------------|-----------------|

|   | FC<br>21      | 2<br>TS<br>I                               | 3<br>FA<br>1038                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4<br>FA<br>1039         | 5<br>FC<br>201     | 6<br>FC<br>201                   | 7               | 8               | 9               | -10      | )               | i             | 12               | 13               | 14               | 16<br>TS<br>2                          | 17<br>TS<br>3                                         | 18<br>TS<br>4                                | 19<br>TS<br>5      | 20<br>TS<br>6                               | 21<br>TS<br>7                | 22<br>FA<br>1028              | 23<br>FA<br>1027                 | . 24                          | 25                 | 26<br>TS<br>8              | 27<br>TS<br>9              | 28<br>FB<br>152                                             | 29<br>FC<br>21     |                  |                  |                              |                            |                  |                   |                   |    |                  |                  |                      |                      |                      |                 |

|   | +3V REGULATOR | I/O CHANNEL O<br>TERMINAL STRIP            | I/O CHANNEL B#1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | I/O CHANNEL B#2         | 10 I/O SUBCHANNELS | 10 I/O SUBCHANNELS               |                 |                 |                 |          |                 |               |                  |                  |                  | I/O CHANNEL 2<br>TERM. STRIP (IN NO. 3 | ESS, NO PACK USED) SYSTEM STATUS, TTYC, TDC, I/O UNIT | TERMINAL STRIP TEST SET CONN (20 DEDOCESCOD) | TEST SET CONN      | CONTROL PANEL                               | CONTROL PANEL TERMINAL STRIP | ERROR REGISTER AND DISPLAY #2 | ERROR REGISTER AND<br>DISPLAY #1 |                               |                    | TEST SET CONN (MICROSTORE) | TEST SET CONN (MICROSTORE) | +I2V REFERENCE AND<br>CONTROL PANEL POWER<br>TERMINAL STRIP | +3V REGULATOR      |                  |                  |                              |                            |                  |                   |                   |    |                  |                  |                      |                      |                      |                 |

|   | I<br>FC<br>21 | 2<br>FC<br>21                              | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4<br>FA<br>1031         | 5<br>FB<br>6       | 6<br>FA<br>1034                  | 7<br>FB<br>6    | 8<br>FB<br>6    | 9<br>FA<br>1010 | )        |                 | I<br>A<br>010 | 12<br>FA<br>1010 | 13<br>FA<br>1010 | 14<br>FA<br>1010 | 16<br>FA<br>1010                       | 17<br>FA                                              |                                              |                    |                                             |                              | 22<br>FA<br>3 1012            | 23<br>FA<br>1015                 | 24<br>FA<br>1012              | 25<br>FA<br>1012   | 26<br>FA<br>1015           | 27<br>FA<br>1012           | 28<br>FA<br>1014                                            | 29<br>FB<br>486    | 31<br>FA<br>1025 | 32<br>FA<br>1019 | 33<br>FA<br>1011             | 34<br>FA<br>1045           | 35<br>FA<br>1021 | 36<br>ED4C<br>063 | 37<br>ED4C<br>065 | 38 | 39<br>ED4<br>069 | 40<br>C ED2H     | 41<br>ED2H<br>042    | 42<br>I ED2H<br>044  | 43<br>ED2H<br>046    | 44<br>.FC<br>21 |

|   | +3V REGULATOR | +3V REGULATOR (IN NO. 3 ESS, NO PACK USED) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-0UT-0F-8 CHECKER (TO) | PROTECTION CKT     | CONSOLE AND 3A CC<br>INTERFACE   | PROTECTION CKT  | PROTECTION CKT  |                 |          | BiT<br>B#1      | SLICE<br>(6)  |                  |                  | •                |                                        | 3IT SL<br>3#1(3                                       |                                              | # MICROCONTROL B#5 | BUS PARITY CHECKER                          |                              | DM<br>(4                      | )<br>                            |                               |                    | DM<br>(4                   | L 0<br>)                   |                                                             | CRYSTAL OSCILLATOR | CLOCK (3A cc)    | MICROCONTROL B#4 | 4-OUT-OF-8 DECODER<br>(FROM) | 4-0UT-OF-8 DECODER<br>(TO) | MICROCONTROL B#6 |                   |                   | 1  |                  | DSTORE<br>5 16-3 | ı)<br>               | 1                    |                      | +3V REGULATOR   |

|   | I<br>FC<br>21 | 2<br>FA<br>1031                            | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4<br>FB<br>6            | 5<br>FA<br>1040    | 6<br>FA<br>1040                  | 7<br>FA<br>1040 | 8<br>FA<br>1024 | 9<br>FA<br>1024 | 16<br>F: | 0<br>A<br>24 10 | 1<br>A<br>124 | 12<br>FA<br>1024 | 13<br>FA<br>1024 | 14<br>FC<br>21   | 16<br>FA<br>1024                       | 17<br>FA<br>102                                       | 18<br>FA<br>1 1024                           | 19<br>FA<br>1030   | 20<br>FA<br>1030                            | 21<br>FA<br>1029             | 22<br>FA<br>1029              | 23<br>FA<br>1046                 | 24<br>FA<br>1033              | 25<br>FA<br>1032   | 26<br>FC<br>202            | 27<br>FA<br>1037           | 28<br>FA<br>1036                                            | 29<br>FA<br>1035   | 31<br>FA<br>1023 | 32<br>FA<br>1022 | 33<br>FA<br>1018             | 34<br>FA<br>1017           | 35<br>FA<br>1016 | 36<br>ED4C<br>062 | 37<br>ED4C<br>064 | 38 | 39<br>ED4<br>068 | C ED21           | 41<br>HI ED2H<br>041 | 42<br>I ED2HI<br>043 | 43<br>I ED2HI<br>045 | 44<br>FC<br>21  |

|   | +3V REGULATOR | 4-CUT-OF-8 CHECKER<br>(FROM)               | and the same of th | PROTECTION CIRCUIT      | INTE               | I SDR1<br>ERFACE<br>26-B1T<br>RE |                 |                 | — в             | IT SL    | ICE B           | <b>‡2 (6</b>  | ) —              | •                | +3V REGULATOR    |                                        | 3iT SL<br>3∰2 (3                                      | ICE                                          |                    | MISCELLANEOUS DECODER<br>AND BIT SLICE HIGH |                              | MAIN MEMORY<br>CONTROL        | DOUBLE STORE READ                | PROGRAM AND TIMER<br>COUNTERS | MISCELLANEOUS CKTS | MAINTENANCE INTERFACE      | MTCE CHANNEL B#3           | MTCE CHANNEL B#2                                            | MTCE CHANNEL B#1   | MICROCONTROL B#8 | MICROCONTROL B#7 | MICROCONTROL B#3             | MICROCONTROL B#2           | MICROCONTROL B#1 |                   |                   | ,  |                  | OSTORE<br>S 0-15 |                      |                      |                      | REGULATOR       |

REPRESENTS

12-1NCH

MOUNTING

PLATE

REPRESENTS

80C

APPARATUS

HOUSING

Fig. 8—3A CC Circuit Pack Locations

Fig. 9—FA-Type Circuit Pack

4.05 All 3A instructions have odd parity with two parity bits over each 16-bit word. The two parity bits of each word are parity (PL) on the low eight bits (0 through 7) and parity (PH) on the high eight bits (8 through 15).

- 4.06 The BA bit is used in the program transfer or branch process. When a branch instruction occurs, a hardware check ensures that the BA bit of the next instruction is set. If for some reason the BA bit is not set, an error is indicated in the 3A CC error register.

- 4.07 The 7-bit OP code field in all instructions specifies the function to be performed. The OP code is used to access a set of microinstructions which accomplish the function indicated by the instruction.

- 4.08 The remaining bits of both single word and double word instructions contain different arrangements and types of information depending on the particular instruction.

#### NO. 2B ESS EMULATED INSTRUCTIONS

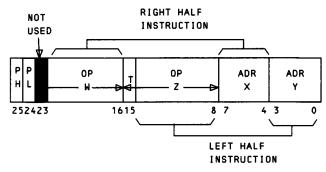

- 4.09 The No. 2B ESS emulated instructions consists of full word instructions and half word instruction (Fig. 16). The half word instructions contain two OP codes and associated address fields and are the most commonly used; however, full word instructions are used when 16 bits of data or a 16-bit address is required in an instruction.

- The basic instruction words are 24 bits long.

The full word instructions contain one instruction with a 7-bit OP code, 16-bit address and a transfer allowed (TA) check bit. This check bit is used for detecting improper transfers because of an equipment fault or an error in program. The number of full word instructions is rather small. They are used for absolute program transfers and also for supplying constants for various functions.

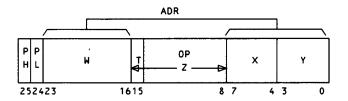

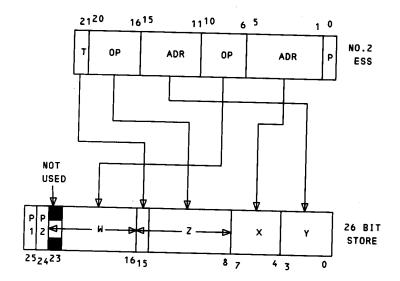

- 4.11 The two half word instructions consists of two 12-bit instructions, each with a 7-bit OP code and a 4-bit address and a TA bit. The 4-bit address is used to denote a value or a modifier. For example, a value associated with a rotate instruction specifies the amount of rotation. A modifier associated with a gating operation specifies the data path from one register to another. The OP code is used to access a set of microinstructions which accomplishes the function indicated by the instruction.

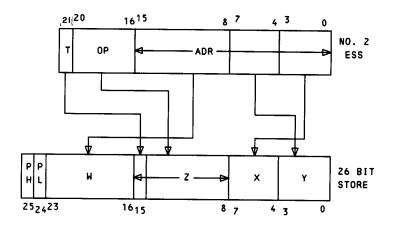

- 4.12 The instruction mapping of half words into the main store is illustrated in Fig. 17. The mapping is not bit for bit. The emulated OP

DISCRETE CIRCUIT PACK

Fig. 10—FC-Type Circuit Pack

A. NAND GATE - SYMBOLIC FORM AND TRUTH TABLE

B. TTL NAND GATE

Fig. 11—NAND Circuit

Fig. 12—Example of Logic Circuit

Fig. 13—Basic Flip-Flop Circuit

B. DOUBLE WORD INSTRUCTION

Fig. 14—3A Instructions

codes are different bit patterns than the old No. 2 OP code bit patterns. Figure 18 illustrates the mapping of a full word instruction into a 26-bit store word.

#### **UNIQUE 2B INSTRUCTIONS**

4.13 The unique 2B instructions consist of full word and half word instructions similar to the No. 2B ESS emulated instructions (Fig. 16). The OP code and address fields of the 2B instructions have the same bit length as the corresponding fields in the emulated instructions. The 2B instructions are formatted and executed exactly like emulated No. 2B instructions.

16

Fig. 15—General Format of 3A Instruction Set

#### 5. FUNCTIONAL DESCRIPTION

# 3A CC FUNCTIONAL RELATIONSHIP TO OTHER SYSTEM UNITS

5.01 The 3A CC is the controlling unit of the 2B processor and the entire system. The 3A CC is duplicated (as well as some other system units) to provide continuous real-time operation with a high degree of system reliability. The 3A CC uses the program instructions and translation data stored in main store to direct and control calls

A. 2B HALF WORD INSTRUCTION

B. 28 FULL WORD INSTRUCTION

Fig. 16—Unique 2B Instructions and No. 2B Emulated Instructions

through the office as well as aid in detecting and analyzing improper performance of the equipment involved in this task. One 3A CC normally has active control over the system while the other 3A CC operates in a standby mode. Each 3A CC has its own dedicated main store. The on-line 3A CC keeps both the on-line and standby memory up-to-date so that the standby 3A CC can assume control of the system if necessary with an up-to-date storage area.

5.02 Since the 3A CC via hardware and software controls the operation of the office, it must be able to communicate with various units within the system. This communication involves the sending and receiving of information to and from other units of the 2B processor and certain peripheral units.

## A. Communication Functions of 3A CC Within the 2B Processor

5.03 The store bus (See Fig. 2) is provided for communication between the 3A CC and the main stores. The functions performed by the 3A CC in relation to the main stores are the reading from or writing into a memory location via the

Fig. 17—Mapping of Two Half Word Instructions Into a 26-Bit Store Word

Fig. 18—Mapping of a Full Word Instruction With a 16-Bit Address Into a 26-Bit Store Word

store bus. The 3A CC main memory control provides the interface between the 3A CC and the store bus. The main store control is covered in detail in 5.48 through 5.64.

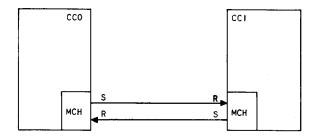

5.04 The 3A CCs must be able to communicate with each other, since the 3A CC is duplicated for system reliability. The maintenance channel (Fig. 19) provides this communication for diagnostic and control unit switching purposes via the maintenance channel (MCH) controller. The MCH is an asynchronous, semiautonomous data transfer system capable of serial ac data transfers at a rate of 6.67 megabits per second. It provides a half-duplex mode (one-way transmission at a time) communication

between the duplicated 3A CCs. The communication is necessary for one 3A CC to determine the state of the other 3A CC and for the on-line 3A CC to exercise the other 3A CC as well. The maintenance channel controller is covered in detail in 5.92 through 5.105.

5.05 The teletypewriter (TTY) and system status panel (SSP) provide an interface between the operating personnel and the system. The 3A CC via a TTY controller communicates with the TTY to perform the functions of outputting characters to the TTY and receiving input characters from the TTY. The 3A CC must also communicate with the SSP to perform the functions of sending

Fig. 19—Maintenance Channel Interconnections

status information to the SSP and receiving manually requested panel operations. Most functions for both TTY and SSP are performed over input/output (I/O) subchannels (see 5.78 through 5.86), however, some SSP functions are hardwired, e.g. FORCE (forces desired CU active).

5.06 The tape data units of the No. 2B ESS provide a backup image of the program and translation data stored in the main stores in case a failure should mutilate the store contents. The 3A CC must communicate with the tape unit to perform the functions of reading data from the tape or writing information on tape. These functions are performed between the 3A CC and the tape unit over an I/O subchannel.

# B. Communication Functions of 3A CC in Relation to Periphery

5.07 The 2B I/O control circuit (Fig. 5), performs the interfacing function between the high-speed processor and the relatively low speed peripheral equipment. The 3A CC has nine miscellaneous decoder control signals and three general purpose registers associated with I/O operations. miscellaneous decoder control signals are generated by the microprogram memory in the 3A CC. These control signals are used in the 2B I/O control circuit to enable gating paths, set or reset flip-flops, or initiate the execution of central pulse distributor or peripheral unit address pulses to control system units which provide service. The 2B I/O control circuit is the buffer circuit through which inputs are received into the processor and from which outputs are transmitted to the peripheral equipment.

Every function performed by the I/O control circuit is initiated by microprogram control leads from the 3A CC. The functions of the 2B I/O control circuit are covered in detail in Section 232-309-108.

#### 3A CC LOGIC UNIT

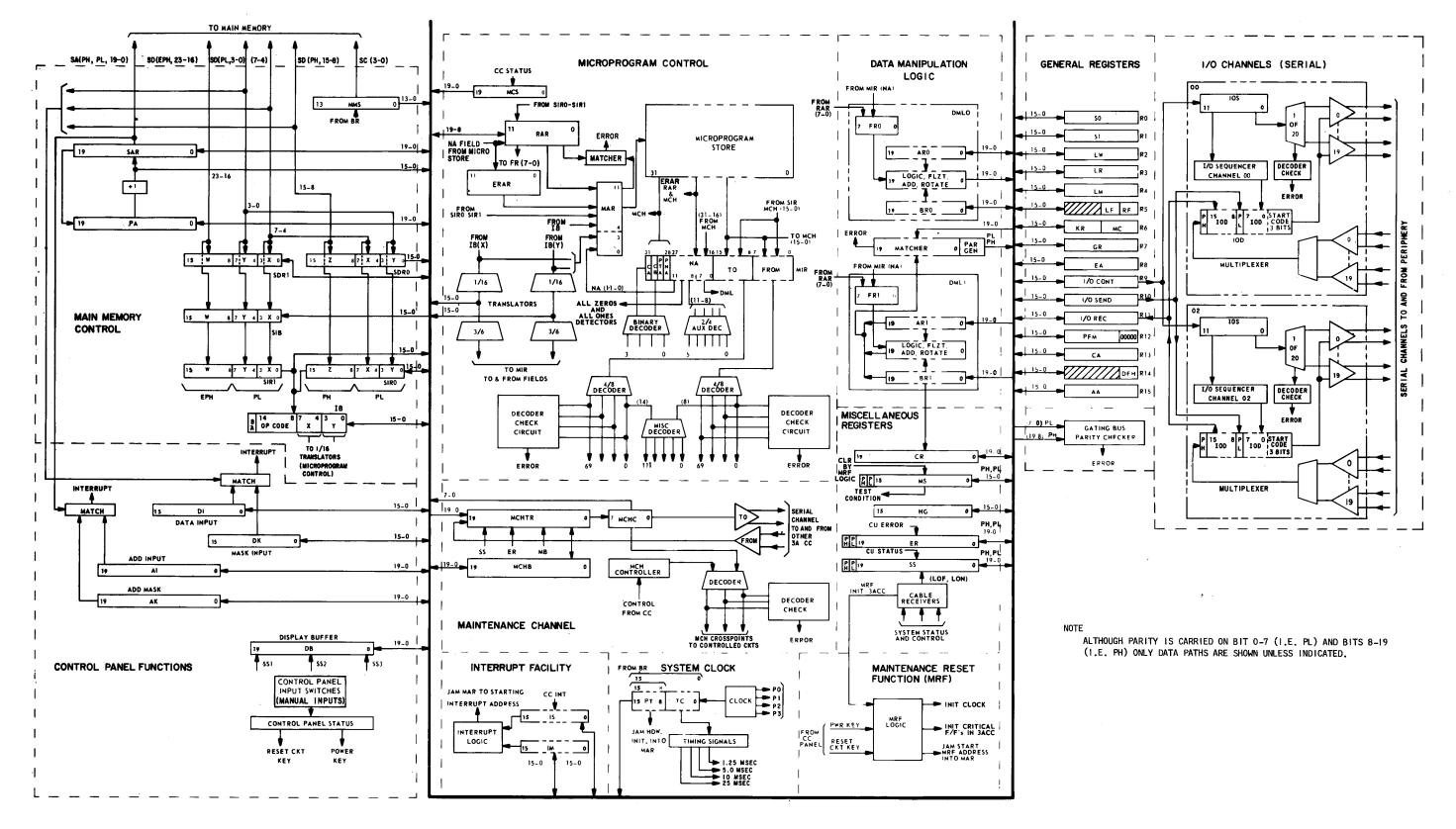

- 5.08 The functional schematic of the 3A CC logic unit is shown in Fig. 20. The schematic has been divided according to functions into the following areas:

- System clock

- 3A CC registers

- Microprogram control

- Main memory control

- Gating bus and bus parity checker

- Data manipulation logic

- I/O channel and controller

- Interrupt facility

- Maintenance channel and maintenance channel controller

- Control panel and control panel functions

- Miscellaneous

The different functional areas will be discussed in a logical sequence which will aid in understanding their relationship of one to another.

#### A. System Clock

- 5.09 The system clock supplies the basic timing pulses necessary to control system functions such as data timing, gate, control, synchronization of events, etc. The system clock generates timing pulses for the 2B I/O control circuit and four sections of the 3A CC:

- Microprogram control

Fig. 20—Functional Schematic of 3A CC

- Main store control

- Maintenance channel controller

- I/O channel sequencer.

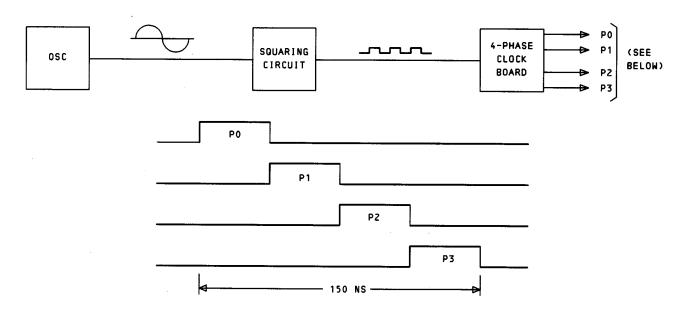

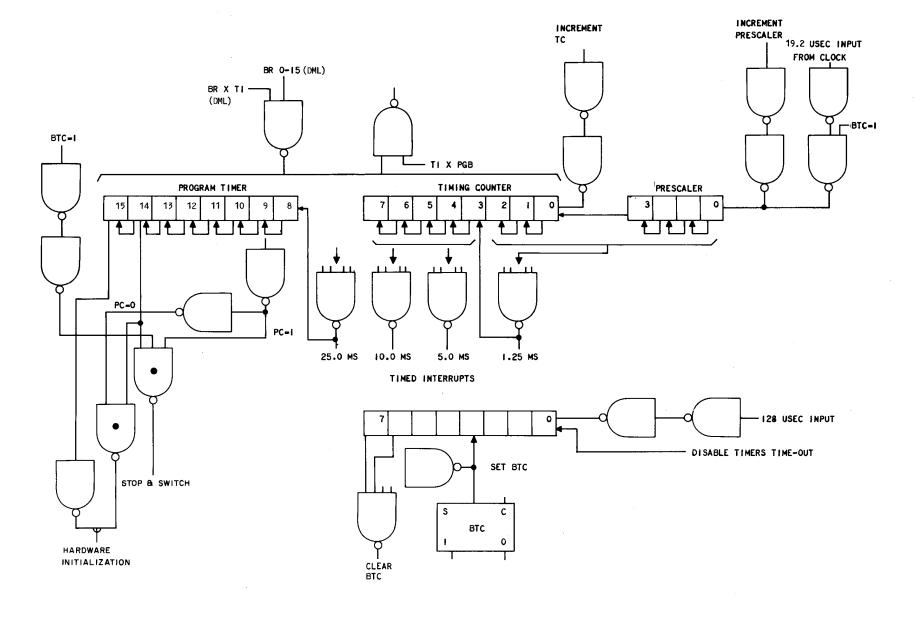

- 5.10 The basic timing signal is generated by a standard crystal oscillator and squaring circuit. The crystal oscillator generates a sine wave with a period of 37.50ns. The sine wave is passed through a squaring circuit to generate a square wave. By the use of a couple of flip-flops and combinational logic, four clock phases are generated (Fig. 21). To provide some additional timing intervals a 10-bit counter is incremented every 150 ns by clock phase P2.

- 5.11 The prescaler, timing counter (TC), and program timer (PT) used in the 3A CC are shown in Fig. 22. Bit 6 of a 10-bit counter (located in the clock) increments the 4-bit prescaler by one every 19.2 usec. The prescaler converts the 19.2 usec clock into a 153.4-usec output which is inputted into the TC to generate the 5 msec timed interrupt. The 25-msec interrupt signal is used to increment the PT. Only the 5-msec signal is wired as an interrupt. The 25-msec signal is used to drive the PT but the 25-msec interrupt is software generated. The 8-bit PT is used in the switching and recovery process of the 3A CC to detect any fault (hardware or software) which causes the 3A CC to stray from the normal execution of its main

- loop. Normally, the PT is updated (reset) before timing to bit 14. It is a function of the software to routinely reset the program timer to prevent initializations. However, if a time-out to bit 14 occurs, the action is dependent on whether the 3A CC is on-line. This time-out may be caused typically by either software or undetected hardware failures.

- 5.12 If the 3A CC is on-line, time-out to bit 14 of the PT causes the 3A CC to stop and send a switch message to the standby 3A CC via the maintenance channel (MCH). The standby 3A CC verifies the switch message, goes on-line, and initializes itself.

- 5.13 If the 3A CC is in standby, time-out to bit 14 causes the standby 3A CC to initialize and restart itself. After restarting, the standby 3A CC checks the status of the on-line 3A CC. If the on-line 3A CC has stopped without sending a switch message, the standby 3A CC will switch on-line and start processing data.

- 5.14 If the PTs are not reset and a time-out to bit 15 occurs in either the on-line or off-line 3A CC, the 3A CC does an initialization and restart. This time-out would occur if the off-line 3A CC was incapable of running and the on-line 3A CC had stopped and sent a switch message to the off-line 3A CC.

Fig. 21—Clock Pulse Waveforms

Fig. 22—Prescaler, Timing Counter, and Program Timer

5.15 If the on-line 3A CC is executing the main loop of its program properly, the PT is set after every completon of the main loop. The on-line PT is loaded with a constant so it will reach its first time-out in 300 msec. At the same time that the on-line 3A CC sets its PT, a command is sent to the standby 3A CC to set its PT. The off-line PT is cleared and will reach its first time-out in 1.6 sec. The on-line 3A CC is set to a constant while the standby 3A CC is set to 0.

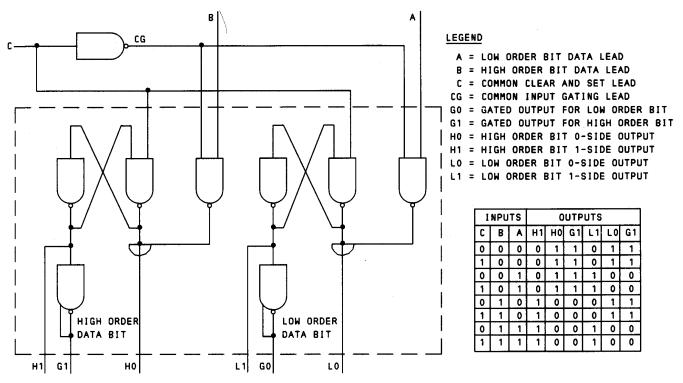

#### B. 3A CC Registers

- 5.16 A register consists of a number of flip-flops which are combined to provide a means of storing data. Each flip-flop can store one bit of information. An example of a 2-bit register cell implemented with 1A logic is shown in Fig. 23. Nine 2-bit register cells are used to form an 18-bit register.

- 5.17 The two basic types of registers in the 3A CC are as follows:

- · General registers

- Special registers.

- 5.18 The general register organization provides for flexibility in data handling and processing. The general registers are designated R0 through R15. Each general register is a 16-bit register with 2 parity bits (parity on bits 0 through 7 and parity on bits 8 through 15). These registers provide a set of general purpose program addressable registers that are used for high-speed buffer storage for data being stored in a current data processing operation.

- 5.19 To formulate 20-bit memory address information, a pair of general registers are utilized. Either registers R12 (bits 0 through 3) and R13 (bits 0 through 15) or R14 (bits 0 through 3) and R15 (bits 0 through 15) can be used in this way.

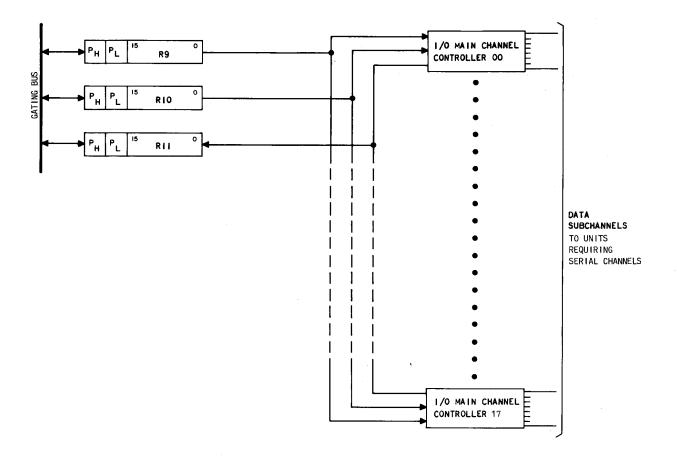

- 5.20 General registers R9, R10, and R11 serve particular functions concerning the I/O:

- (1) R9 as a buffer for the control information to be sent to the I/O facility from the 3A CC

- (2) R10 for the data to be sent to the I/O facility

(3) R11 for the results or data received from the external units via the I/O facilities.

When these registers are not being used for their I/O functions, they are used as general registers.

- 5.21 The special registers are dedicated to specific functions and depending on that function, may vary in length e.g., 20-bit store address register (SAR) and 16-bit store data register (SDR). Only 16 of the special registers may be displayed, loaded, or accessed by operation of the control panel. These procedures are covered in Section 232-306-301. The special registers are used for:

- (1) Microprogram control and sequencing

- (2) Interface to the main store

- (3) Buffering data for microprogram control operations

- (4) Maintenance purposes.

Special registers and their checking schemes are discussed later in this section under their individual applications.

5.22 The general registers and most of the special registers are 2-bit partitioned or 2-bit sliced. This means that two bits of each register are on a single circuit board (Fig. 24), e.g., the first circuit pack contains bits 0 and 8 of every general register. Partitioning is used so that a fault will affect at most only two bits of any register and therefore be detected by the two parity bits.

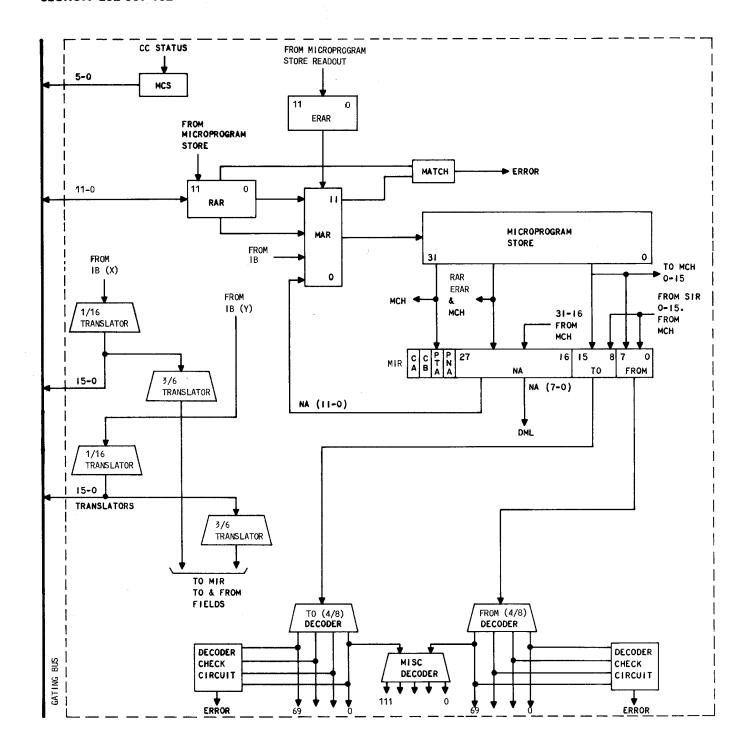

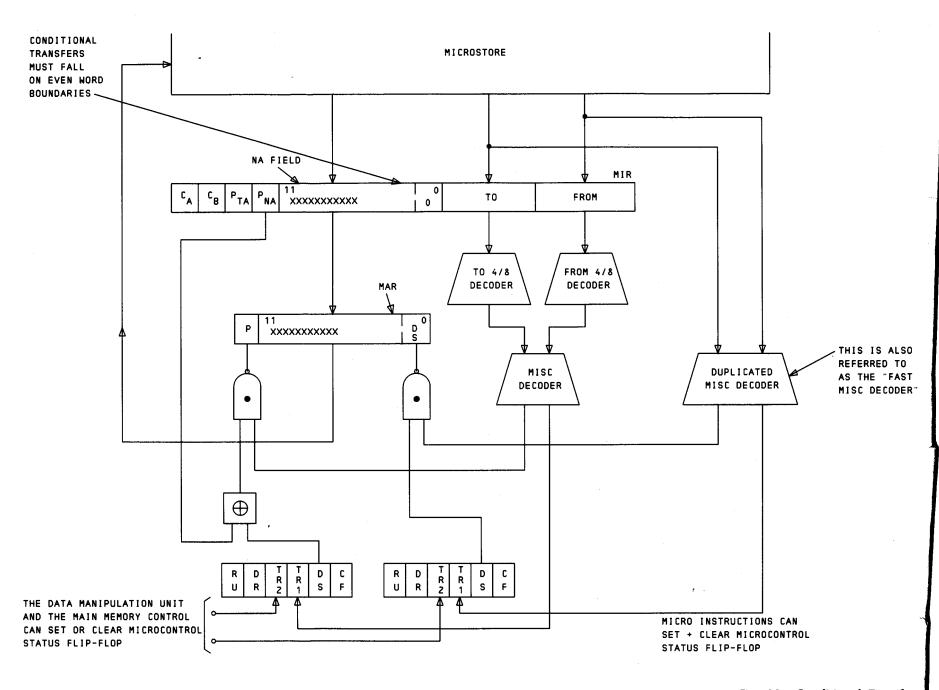

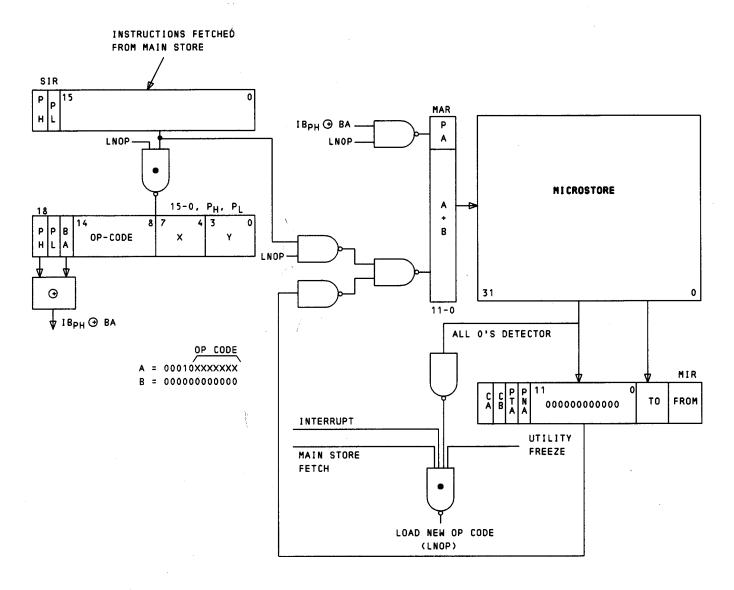

#### C. Microprogram Control

The microprogram control (Fig. 25) acts as a translator. When an instruction is read out of main store, the microprogram control accesses a particular area of microcode in the microstore. The operation (OP) code of the instruction fetched from main store points to the starting address of the sequence of microinstructions (microsequence). The number of microinstructions in a microsequence range from 2 to 25 depending on the complexity of the instruction. The microsequence translates the OP code of the instruction and generates the gating and sequencing required to execute the instruction. Most instructions involve taking information from a register, placing the information on a bus (usually the gating bus) and gating the

NOTE:

TO CLEAR OR SET EITHER BIT, THE C LEAD MUST BE PULSED LOW WITH THE APPROPRIATE SIGNAL ON THE DATA LEAD. COMMON INPUT GATING IS PROVIDED BY CG. TO STORE A BINARY 1 IN THE HIGH ORDER BIT AND/OR LOW ORDER BIT, THE APPROPRIATE DATA LEAD MUST HAVE A HIGH VOLTAGE WHEN A LOW VOLTAGE IS APPLIED TO THE C LEAD. SIMILARLY, TO STORE A BINARY 0, THE APPROPRIATE DATA LEAD MUST HAVE A LOW VOLTAGE WHEN A LOW VOLTAGE IS APPLIED TO THE C LEAD. THE COLLECTORS OF THE INPUT GATES ARE TIED DIRECTLY TO THEIR RESPECTIVE FLIP-FLOP ZERO OUTPUTS TO PROVIDE THE FAST SET FEATURE.

Fig. 23—2-Bit Register Cell

PL = PARITY OVER BITS 0,1,2,3,4,5,6,7

PH = PARITY OVER BITS 8,9,10,11,12,13,14,15

Fig. 24—Layout of General Registers

information to another register. The signals from the TO and FROM decoders control the data transfer operation. The microstore contains many microsequences used not only to translate commands but other functions such as, interrupts, panel operations, program loading, control functions, etc. The microprogram control is made up of the following:

- Microprogram address register

- Microprogram store

- Microinstruction register

- Return address register

- Error return address register

- Decoders and translators

- Microcontrol status register

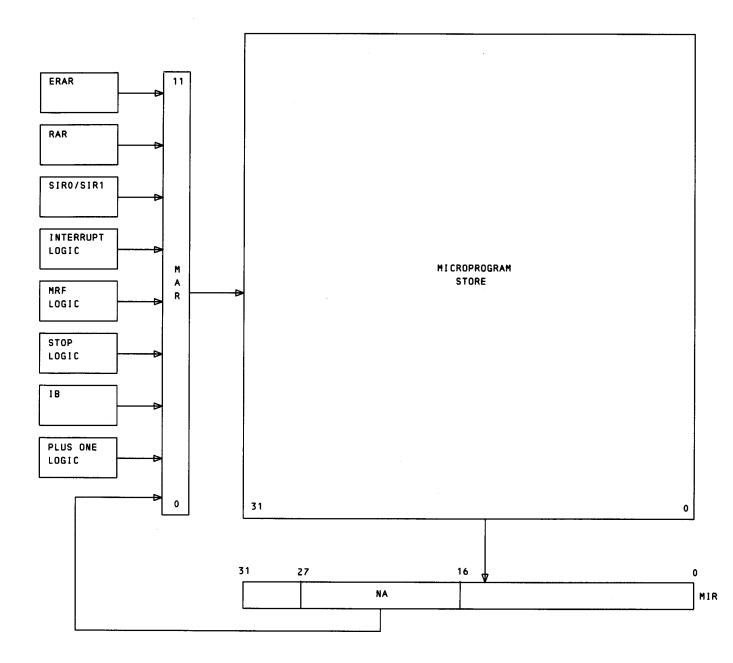

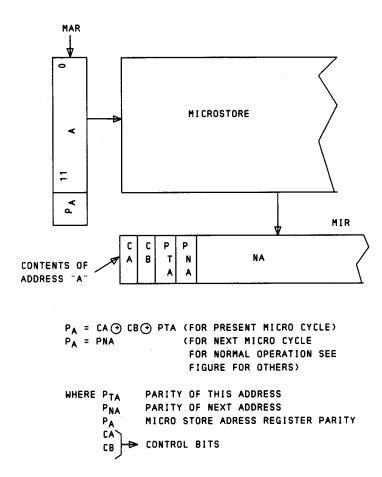

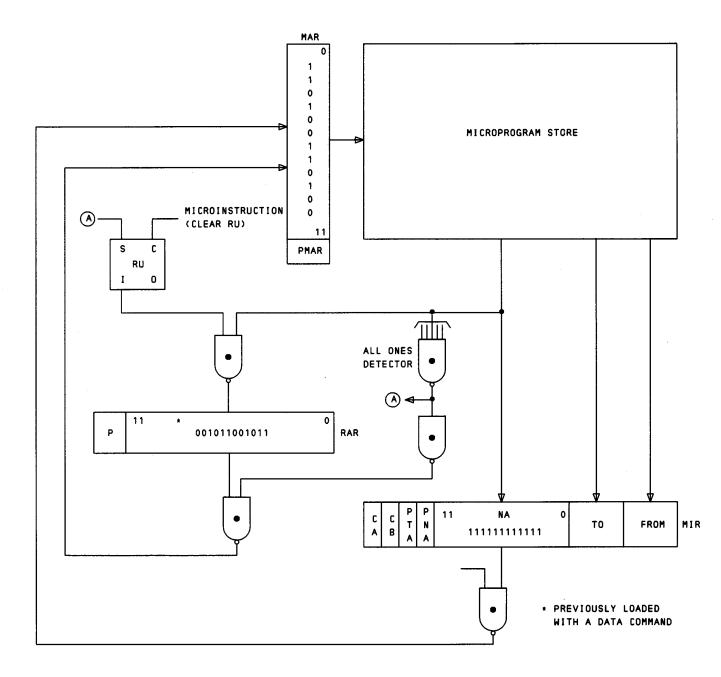

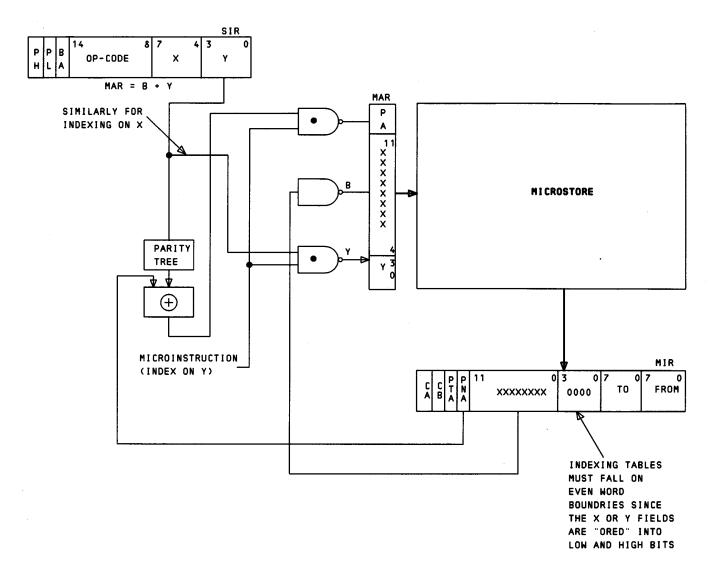

- 5.24 Microprogram Address Register (MAR): The MAR is used to address the microstore. The address may be loaded into the MAR by one of the following (Fig. 26):

- (a) The store instruction registers (SIR0/SIR1) after a main store instruction fetch is completed.

- (b) The next address (NA) field of the microinstruction register (MIR).

- (c) The return address register (RAR) when implementing a subroutine return.

- (d) By incrementing the MAR. One is added to the MAR when the MIR control bits (CA and CB) indicate that the MIR NA field is to be used as data or auxiliary control (see 5.32 and Table A).

- (e) By indexing the MAR by the IB x or y fields.

- (f) Loaded to interrupt starting address.

- (g) Jammed to stop address or initialization (MRF) address.

- (h) The error return address register (ERAR) when implementing microsubroutine return after complement correction.

- **Microstore:** The microstore is a programmable read only memory (PROM) with a maximum access time of 65 nanoseconds (ns). The microstore has a maximum size of 4096 32-bit words. Part of the microstore consists of six circuit packs for storing the 3A microcode. The other part consists of eight circuit packs for storing the 2B microcode. Each circuit pack contains 512 words (16 bits in length). Since each microprogram word is 32 bits in length, two circuit packs are addressed on each microstore cycle. The microstore is growable in increments of 512 words to a maximum size of 4096 words. For each 512 words added, two additional circuit packs are needed. Space is available within the 3A CC to equip the maximum size microstore.

- 5.26 The microcode stored in the microstore cannot be altered by the processor. The only way it can be altered is by replacing a circuit pack with one that is encoded with different information. The microstore is addressed by the MAR and the output is gated to the microinstruction register (MIR).

TABLE A

STATE AND USE THE TWO CONTROL BITS IN MICROINSTRUCTION REGISTER

| CA | СВ | STATE                           | USE                                                                                                                                                                                                                         |

|----|----|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0  | 0  | Null or Normal                  | Normal sequencing where no control function is required and the NA field is gated to the MAR.                                                                                                                               |

| 0  | 1  | Main Store Instruction<br>Fetch | Initiates a new main store operation.                                                                                                                                                                                       |

| 1  | 0  | Data Control                    | Inhibits the normal sequencing and jams a one into bit zero of the last microstore address in the MAR. This is for data operations. The NA field contains data to be gated to some destination register other than the MAR. |

| 1  | 1  | Auxiliary Control               | Enables an auxiliary decoder attached to the upper four bits of the NA field.                                                                                                                                               |

Fig. 25—Microprogram Control Block Diagram

5.27 Microinstruction Register (MIR): The MIR is a 32-bit register used to buffer microinstructions which are gated out of the microstore. The MIR contains a FROM field (bits 0 through 7), a TO field (bits 8 through 15), a NEXT ADDRESS (NA) field (bits 16 through 27),

two parity bits (bits 28 and 29), and a two bit control field (bits 30 and 31).

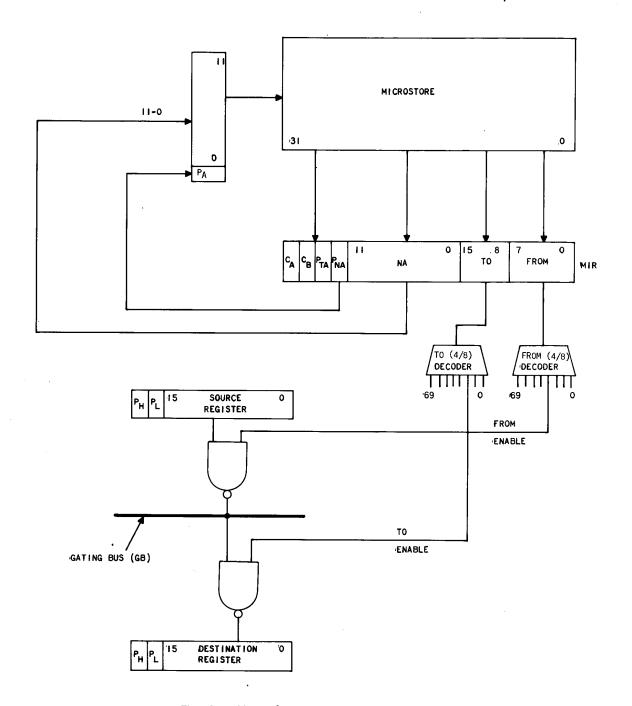

5.28 The basic instruction set consists of register-to-register gating operations (Fig. 27). The register gating operation is implemented

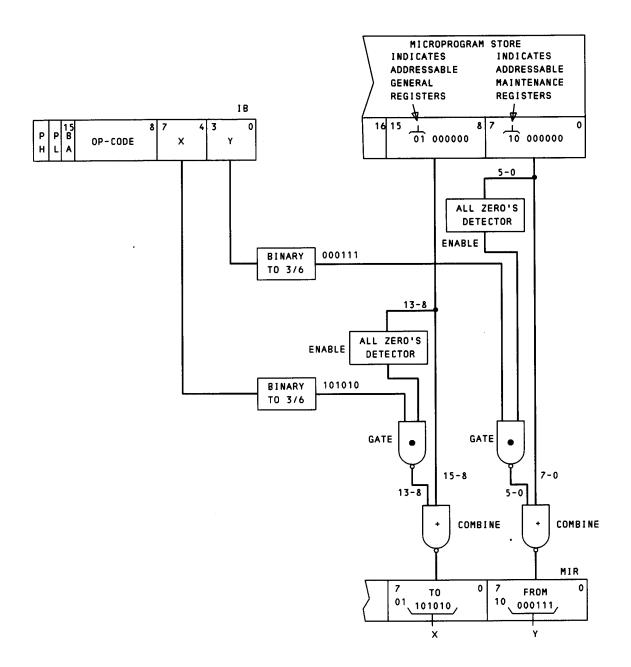

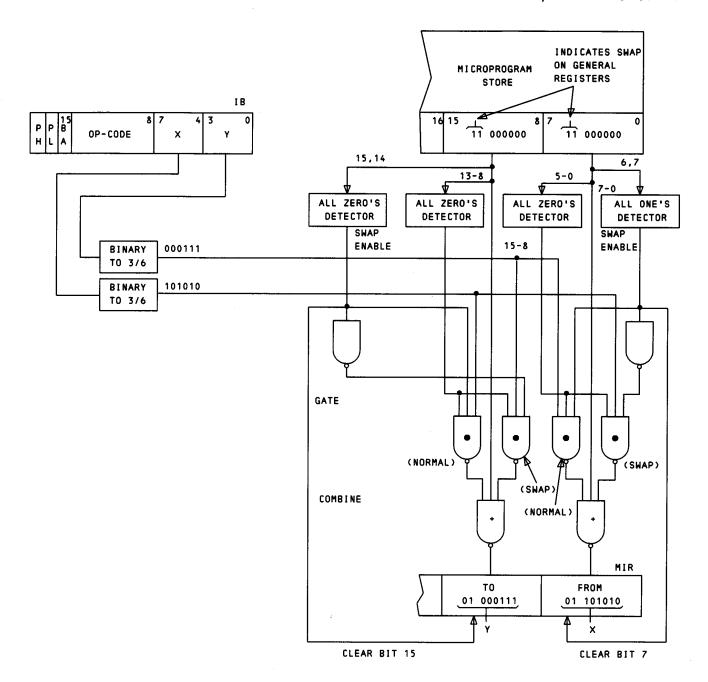

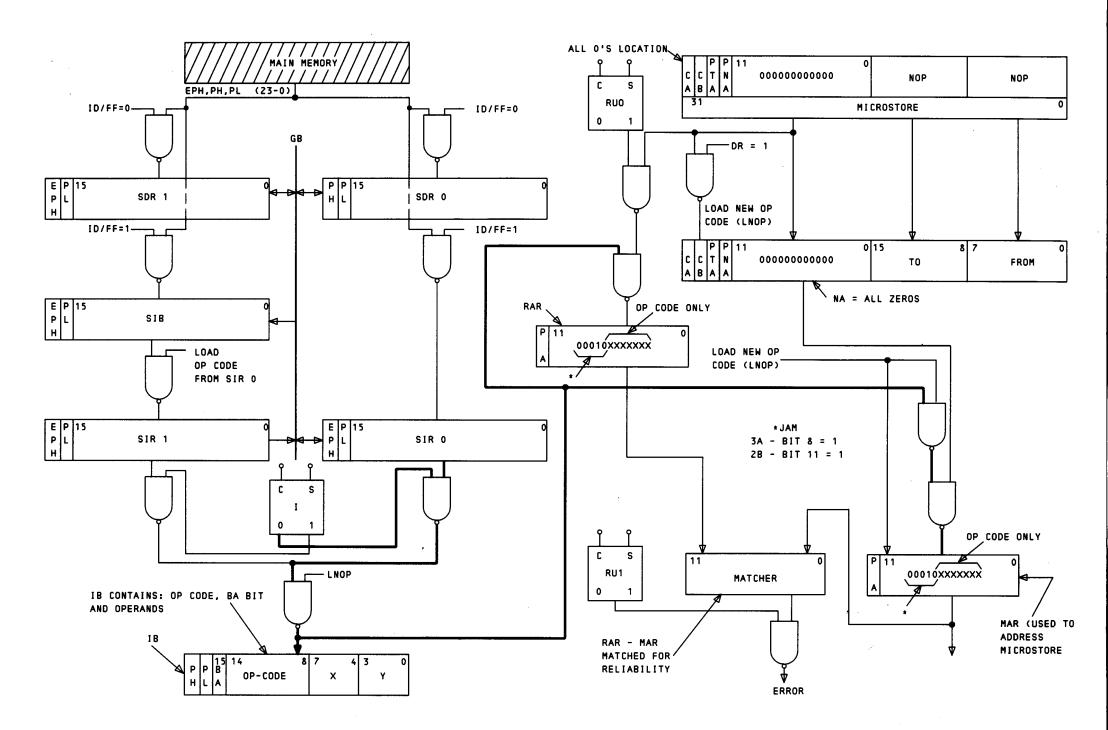

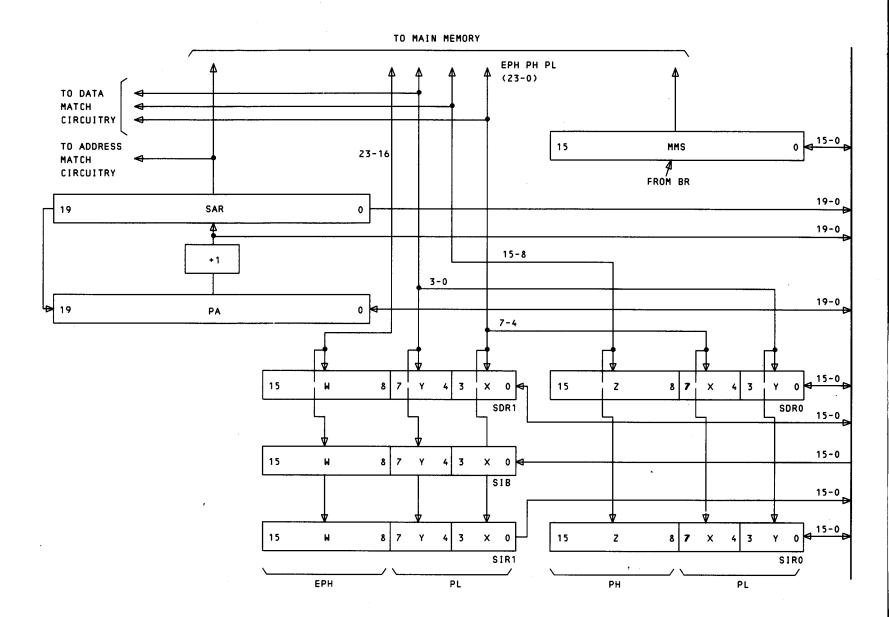

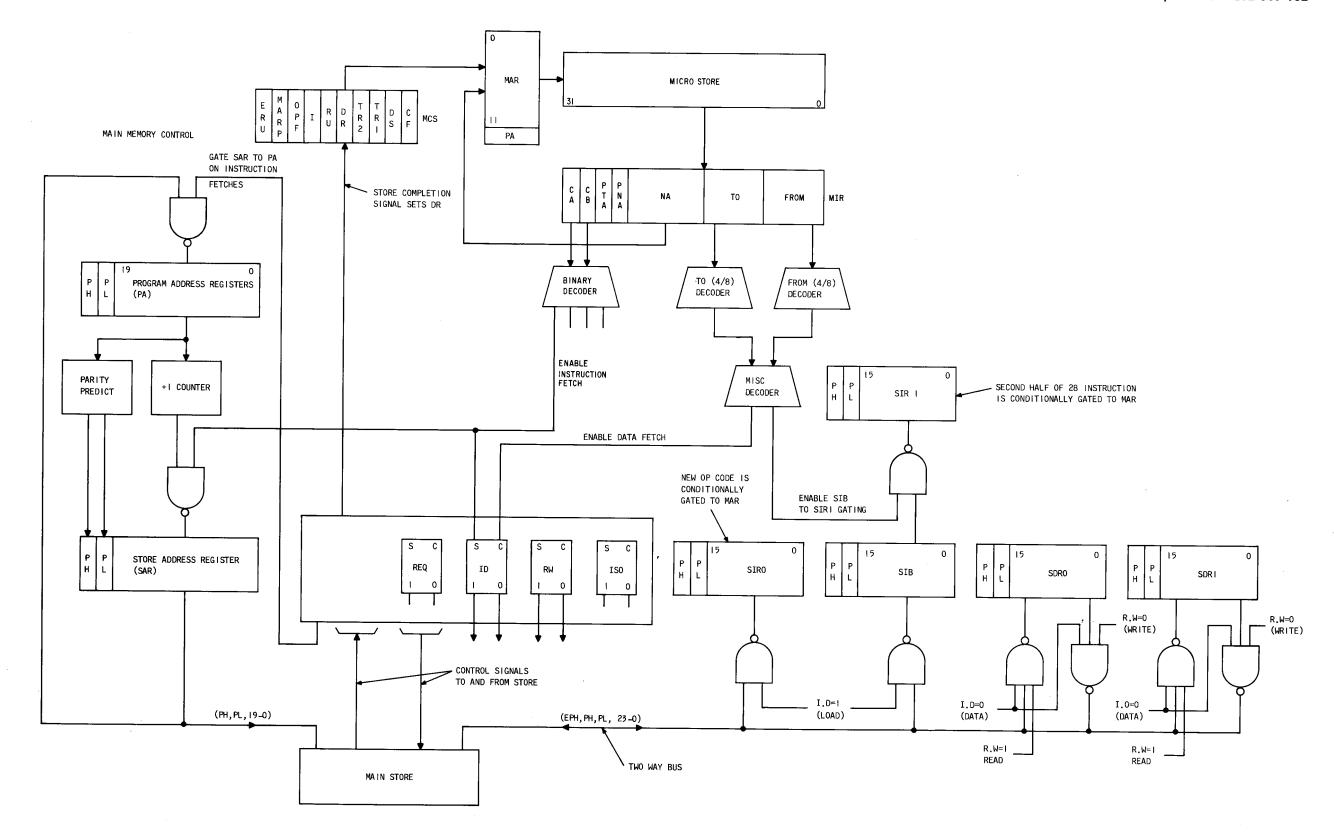

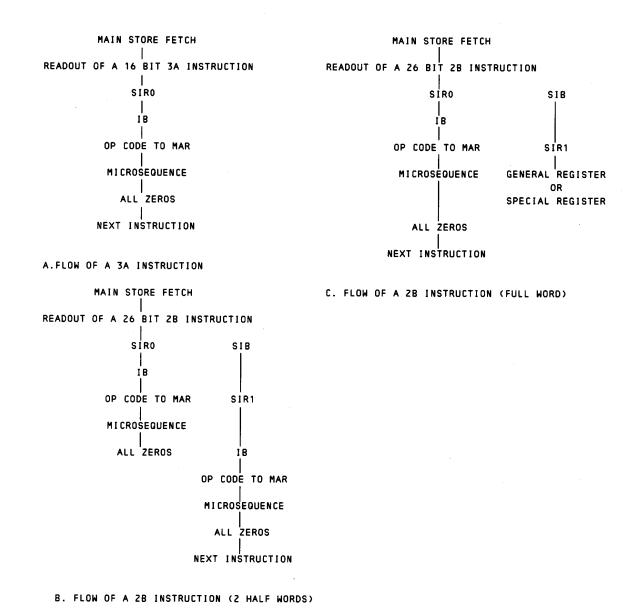

Fig. 26—Loading of Microaddress Register